- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358972 > M24C64-WMN6T (意法半導(dǎo)體) 18-Bit Universal Bus Transceiver With 3-State Outputs 56-SSOP -40 to 85 PDF資料下載

參數(shù)資料

| 型號: | M24C64-WMN6T |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 18-Bit Universal Bus Transceiver With 3-State Outputs 56-SSOP -40 to 85 |

| 中文描述: | 64Kbit和32Kbit串行IC總線的EEPROM |

| 文件頁數(shù): | 5/26頁 |

| 文件大小: | 394K |

| 代理商: | M24C64-WMN6T |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

5/26

M24C64, M24C32

SIGNAL DESCRIPTION

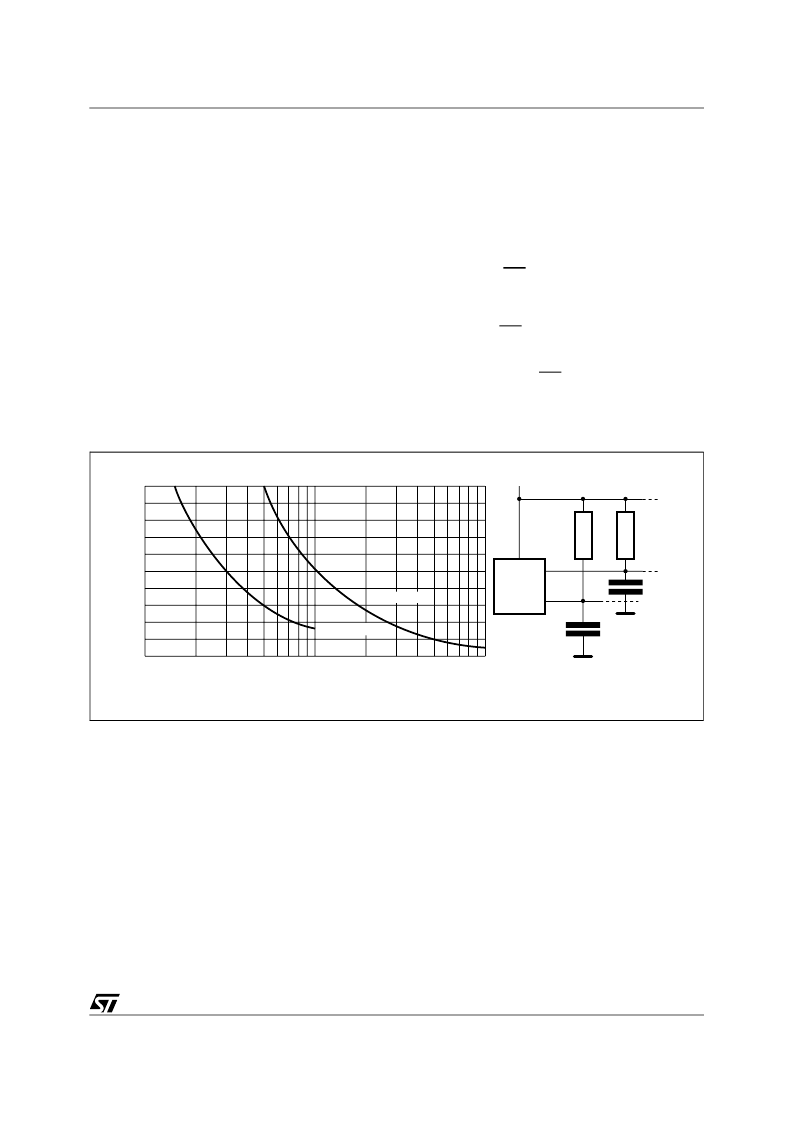

Serial Clock (SCL).

This input signal is used to

strobe all data in and out of the device. In applica-

tions where this signal is used by slave devices to

synchronize the bus to a slower clock, the bus

master must have an open drain output, and a

pull-up resistor must be connected from Serial

Clock (SCL) to V

CC

. (

Figure 4.

indicates how the

value of the pull-up resistor can be calculated). In

most applications, though, this method of synchro-

nization is not employed, and so the pull-up resis-

tor is not necessary, provided that the bus master

has a push-pull (rather than open drain) output.

Serial Data (SDA).

This bi-directional signal is

used to transfer data in or out of the device. It is an

open drain output that may be wire-OR’ed with

other open drain or open collector signals on the

bus. A pull up resistor must be connected from Se-

rial Data (SDA) to V

CC

. (

Figure 4.

indicates how

the value of the pull-up resistor can be calculated).

Chip Enable (E0, E1, E2).

These input signals

are used to set the value that is to be looked for on

the three least significant bits (b3, b2, b1) of the 7-

bit Device Select Code. These inputs must be tied

to V

CC

or V

SS

, to establish the Device Select

Code.

Write Control (WC).

This input signal is useful

for protecting the entire contents of the memory

from inadvertent write operations. Write opera-

tions are disabled to the entire memory array when

Write Control (WC) is driven High. When uncon-

nected, the signal is internally read as V

IL

, and

Write operations are allowed.

When Write Control (WC) is driven High, Device

Select and Address bytes are acknowledged,

Data bytes are not acknowledged.

Figure 4. Maximum R

L

Value versus Bus Capacitance (C

BUS

) for an I

2

C Bus

AI01665

VCC

CBUS

SDA

RL

MASTER

RL

SCL

CBUS

100

0

4

8

12

16

20

CBUS (pF)

M

)

10

1000

fc = 400kHz

fc = 100kHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M24C64-MB3TP | 16-Bit Transparent D-Type Latch With 3-State Outputs 54-BGA MICROSTAR JUNIOR -40 to 85 |

| M24C64-MB6 | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-TSSOP -40 to 85 |

| M24C64-MB6P | 16-Bit Transparent D-Type Latch With 3-State Outputs 56-BGA MICROSTAR JUNIOR -40 to 85 |

| M24C64-MB6T | 16-Bit Transparent D-Type Latch With 3-State Outputs 54-BGA MICROSTAR JUNIOR -40 to 85 |

| M24C64-MB6TP | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-TSSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M24C64WMN6TP | 制造商:ST MICRO 功能描述:Pb Free |

| M24C64-WMN6TP | 功能描述:電可擦除可編程只讀存儲器 電可擦除可編程只讀存儲器 S. I2C 64k RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24C64-WMN6TP/P | 制造商:STMicroelectronics 功能描述:EEPROM SERL-I2C 64KBIT 8KX8 3.3V/5V 8PIN SO N - Tape and Reel |

| M24C64-WMN6TP-CUT TAPE | 制造商:ST 功能描述:M24C64 Series 64 Kb (8 K x 8) 2.5 V SMT Serial I? Bus EEPROM - SOIC-8 |

| M24D16161DA | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:16-Mbit (1M x 16) Pseudo Static RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。