- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359070 > M48Z58Y-70PC6TR (意法半導體) 64 Kbit 8Kb x 8 ZEROPOWER SRAM PDF資料下載

參數(shù)資料

| 型號: | M48Z58Y-70PC6TR |

| 廠商: | 意法半導體 |

| 英文描述: | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| 中文描述: | 64千位的8kB × 8 ZEROPOWER的SRAM |

| 文件頁數(shù): | 7/17頁 |

| 文件大小: | 133K |

| 代理商: | M48Z58Y-70PC6TR |

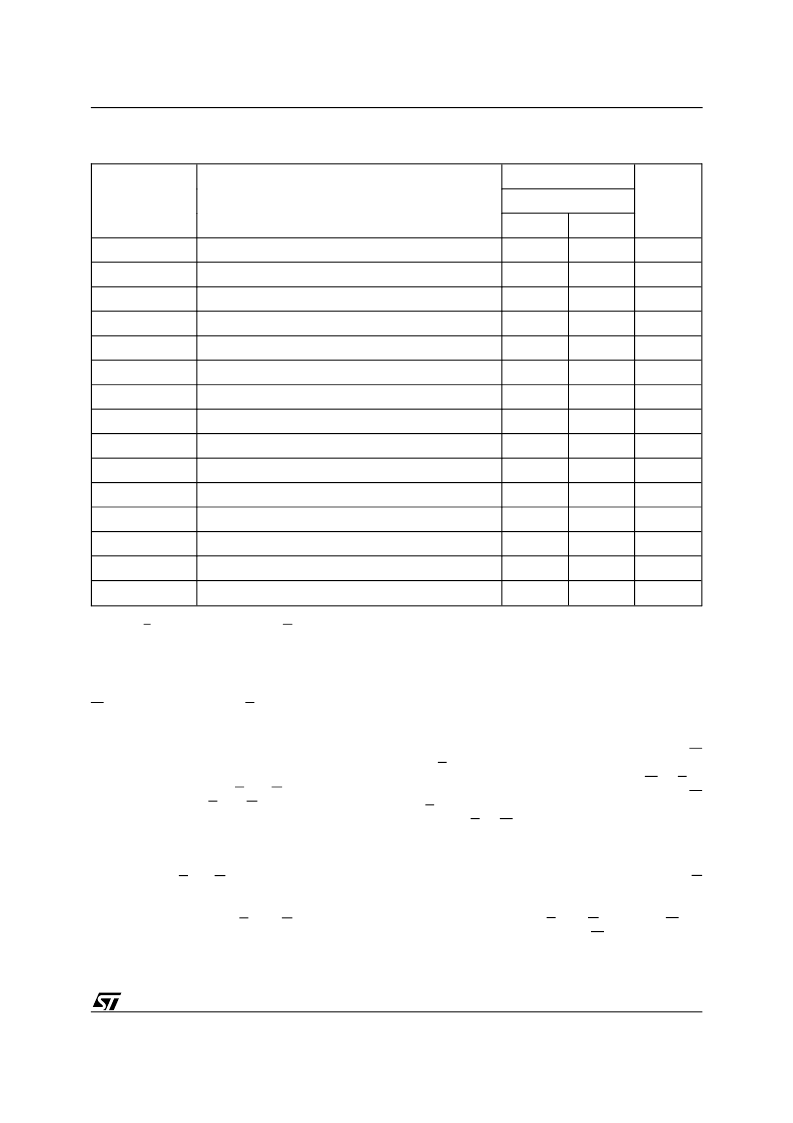

Symbol

Parameter

M48Z58 / M48Z58Y

Unit

-70

Min

Max

t

AVAV

Write Cycle Time

70

ns

t

AVWL

Address Valid to Write Enable Low

0

ns

t

AVEL

Address Valid to Chip Enable Low

0

ns

t

WLWH

Write Enable Pulse Width

50

ns

t

ELEH

Chip Enable Low to Chip Enable High

55

ns

t

WHAX

Write Enable High to Address Transition

0

ns

t

EHAX

Chip Enable High to Address Transition

0

ns

t

DVWH

Input Valid to Write Enable High

30

ns

t

DVEH

Input Valid to Chip Enable High

30

ns

t

WHDX

Write Enable High to Input Transition

5

ns

t

EHDX

Chip Enable High to Input Transition

5

ns

t

WLQZ

(1, 2)

Write Enable Low to Output Hi-Z

25

ns

t

AVWH

Address Valid to Write Enable High

60

ns

t

AVEH

Address Valid to Chip Enable High

60

ns

t

WHQX

(1, 2)

Write Enable High to Output Transition

5

ns

Notes:

1. C

L

= 5pF (see Figure 4).

2. If E goes low simultaneously with W going low, the outputs remain in the high impedance state.

Table 10. Write Mode AC Characteristics

(T

A

= 0 to 70

°

C or –40 to 85

°

C; V

CC

= 4.75V to 5.5V or 4.5V to 5.5V)

READ MODE

The M48Z58/58Y is in the Read Mode whenever

W (Write Enable) is high, E (Chip Enable) is low.

Thus, the unique address specified by the 13 Ad-

dress Inputs defines which one of the 8,192 bytes

of data is to be accessed. Valid data will be avail-

able at the Data I/O pins within Address Access

time (t

AVQV

) after the last address input signal is

stable, providing that the E and G access times are

also satisfied. If the E and G access times are not

met, valid data will be available after the latter of

the Chip Enable Access time (t

ELQV

) or Output

Enable Access time (t

GLQV

).

The state of the eight three-state Data I/O signals

is controlled by E and G. If the outputs are activated

before t

AVQV

, the data lines will be driven to an

indeterminate state until t

AVQV

. If the Address In-

puts are changed while E and G remain active,

output data will remain valid for Output Data Hold

time (t

AXQX

) but will go indeterminate until the next

Address Access.

WRITE MODE

The M48Z58/58Y is in the Write Mode whenever W

and E are low. The start of a write is referenced

from the latter occurring falling edge of W or E. A

write is terminated by the earlier rising edge of W

or E. The addresses must be held valid throughout

the cycle. E or W must return high for a minimum

of t

EHAX

from Chip Enable or t

WHAX

from Write

Enable prior to the initiation of another read or write

cycle. Data-in must be valid t

DVWH

prior to the end

of write and remain valid for t

WHDX

afterward. G

should be kept high during write cycles to avoid bus

contention; although, if the output bus has been

activated by a low on E and G, a low on W will

disable the outputs t

WLQZ

after W falls.

7/17

M48Z58, M48Z58Y

相關PDF資料 |

PDF描述 |

|---|---|

| M48Z58YMH | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M491B | SINGLE-CHIP VOLTAGE SYNTHESIS TUNING SYSTEM WITH 1 ANALOG CONTROL |

| M491B1 | SINGLE-CHIP VOLTAGE SYNTHESIS TUNING SYSTEM WITH 1 ANALOG CONTROL |

| M494 | SINGLE-CHIP VOLTAGE TUNING SYSTEM WITH 4 ANALOG CONTROLS AND mP INTERFACE |

| M4TXX-BR12 | TIMEKEEPER SNAPHAT Battery & Crystal |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M48Z58YMH | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M48Z58YPC | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M48Z58YSH | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M49 | 制造商:MERCURY 制造商全稱:MERCURY 功能描述:Surface Mount Crystals |

| M-490 | 制造商:Apex Tool Group 功能描述:HEX DRIVE BIT HOLDER 制造商:APEX 功能描述:HEX DRIVE BIT HOLDER; Length:75mm; For Use With:Apex 1/4" Hex Inserts; Bit Type:Hex; Size:1/4" Hex ;RoHS Compliant: NA |

發(fā)布緊急采購,3分鐘左右您將得到回復。