- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370991 > M65617 (Mitsubishi Electric Corporation) PICTURE-IN-PICTURE SIGNAL PROCESSING PDF資料下載

參數(shù)資料

| 型號(hào): | M65617 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | PICTURE-IN-PICTURE SIGNAL PROCESSING |

| 中文描述: | 子母圖像信號(hào)處理 |

| 文件頁(yè)數(shù): | 7/15頁(yè) |

| 文件大小: | 74K |

| 代理商: | M65617 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

MITSUBISHI ICs (TV)

M65617SP

PICTURE-IN-PICTURE SIGNAL PROCESSING

7

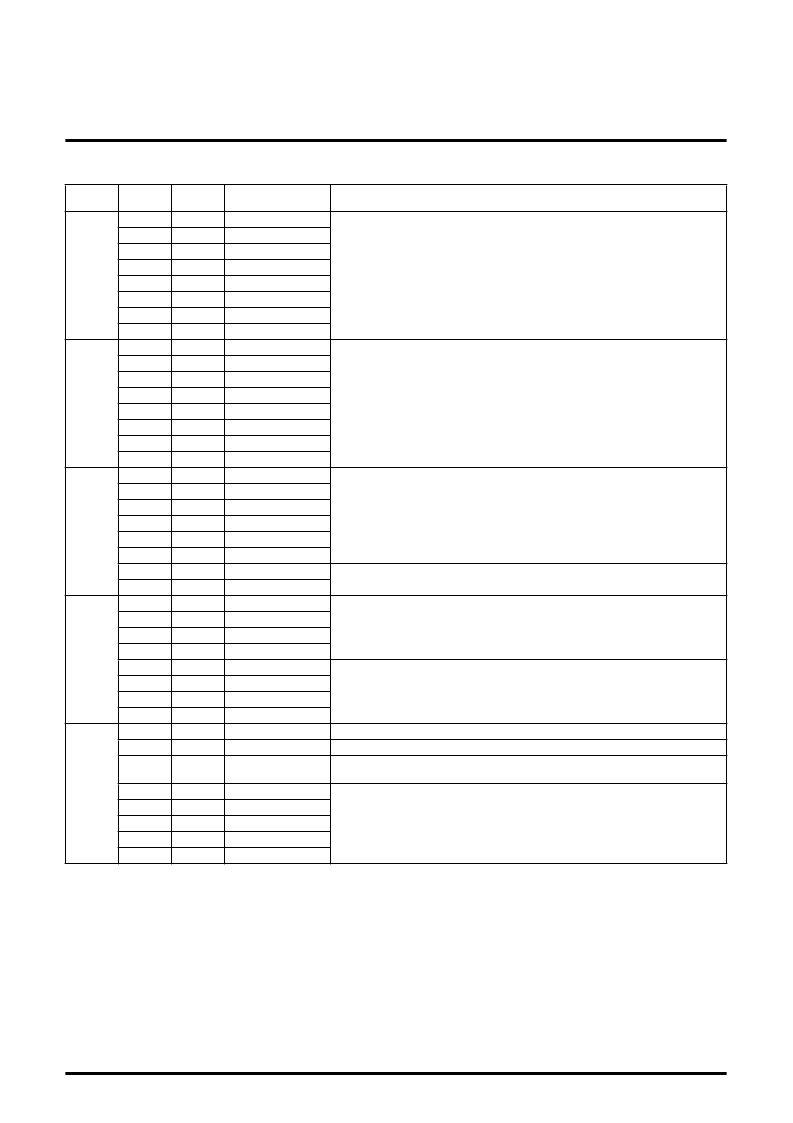

SERIAL REGISTER INFORMATION

(cont.)

Sub-

address

setting

0

0/1

1

0/1

2

1/0

3

0/0

4

0/1

5

0/1

6

1/0

7

0/0

0

0/0

1

0/0

2

0/0

3

1/0

4

0/1

5

0/0

6

0/0

7

0/0

0

0/1

1

0/0

2

0/0

3

1/1

4

1/0

5

1/1

6

7

0

1

2

3

4

5

6

7

0

1

Bit No.

Reference

Register name

Function

0Bh

vya (0)

vya (1)

vya (2)

vya (3)

vya (4)

vya (5)

vya (6)

vya (7)

hxa (0)

hxa (1)

hxa (2)

hxa (3)

hxa (4)

hxa (5)

hxa (6)

hxa (7)

hya (0)

hya (1)

hya (2)

hya (3)

hya (4)

hya (5)

ext-bhsel (0)

ext-bhsel (1)

adj (0)

adj (1)

adj (2)

adj (3)

hadj (0)

hadj (1)

hadj (2)

hadj (3)

disp

bgc

Setting of display period (vertical);

{vya<7:0>} line

[44h/33h (1/9-1/16 sizes)]

0Ch

Setting of display start position (horizontal);

{hxa0<7:0>

×

4

×

70ns+12.8}us

[08h-10h (1/9-1/6 sizes) when displayed at the upper left]

0Dh

Setting of display period (horizontal);

{(hya0<5:0>-1)

×

4

×

70}us

[38h/29h (1/9 - 1/16 sizes)]

1

1

0

0

1

0

1

1

1

1

1

0

Selection of sync input for burst clock;

HD pin [0 or 1], VD pin [2], internal analog [3] [3 setting]

0Eh

Adjustment of sub-screen display-starting horizontal position; [4h setting]

70ns/step

Min. 280ns [0h], center 0ns [4h], +770ns [Fh]

Adjustment of supplementary BGP position; [Normally Fh setting]

Parameter to adjust PIP Y output signal clamping position to main Y input signal

pedestal (when 03h<4>(bgpmsel) = 1)

5.6us[0h], 6.6us [Fh] (pulse width: 2.6us) from the front end of horizontal sync

0Fh

Display control; PIP display OFF/ON [0/1] (ineffective at background)

Background display control; OFF/ON [0/1]

Authorization of addition of sync when missing main source is detected; OFF/

ON [0/1]

2

0

dofc

3

4

5

6

7

1

1

1

1

0

y-offset (0)

y-offset (1)

y-offset (2)

y-offset (3)

y-offset (4)

Setting of luminance signal output DC offset;

Set pedestal level within a range of 32 digits/256 digits (complements of 2, "-16fl

to +15fl" or "0", provides image data bottom values. It serves fine adjustment of

brightness.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M65617SP | PICTURE-IN-PICTURE SIGNAL PROCESSING |

| M65675FP | DIGITAL NTSC/PAL ENCODER |

| M65676FP | DIGITAL NTSC/PAL ENCODER |

| M65677FP | DIGITAL NTSC/PAL ENCODER |

| M65727FP | MPEG2 MOTION ESTIMATION LSI |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M65617SP | 制造商:Panasonic Industrial Company 功能描述:CONTROLLER |

| M65656FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SCAN CONVERTER |

| M65657FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SCAN CONVERTER |

| M65664FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:PICTURE-IN-PICTURE SIGNAL PROCESSING |

| M65665 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:PICTURE-IN-PICTURE SIGNAL PROCESSING |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。