- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370992 > M66515FP (Mitsubishi Electric Corporation) LASER-DIODE DRIVER/CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | M66515FP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | LASER-DIODE DRIVER/CONTROLLER |

| 中文描述: | 激光二極管驅(qū)動(dòng)器/控制器 |

| 文件頁數(shù): | 3/7頁 |

| 文件大小: | 174K |

| 代理商: | M66515FP |

3

MITSUBISHI

DIGITAL ASSP

M66515FP

LASER-DIODE DRIVER/CONTROLLER

OPERATION

1. Laser Drive Currents

The approximate values of laser drive currents, I

SW

and I

B

,

are obtained by the following equation, in which V

C

is the volt-

age of holding capacitor connected to the C

H

pin.

(1) I

SW

(switching current)

V

C

[V]

R

S

[k

]

I

SW

[mA] = 12

×

provided that 0

≤

V

C

≤

V

CC

– 1.8V and I

SW (max.)

=120mA

where R

S

is the resistance of the resistor connected between

the R

S

pin and GND.

(2) I

B

(bias current)

V

B

[V]

R

B

[k

]

I

B

[mA] = 10

×

provided that 0

≤

V

B

≤

Vcc – 2.7V and I

B (max.)

= 30mA

where R

B

is the resistance of the resistor connected between

the R

B

pin and GND.

2. Switching Operation

If DATA = “L,” the LD drive current is I

SW

+ I

B

; if DATA = “H,”

I

B

.

3. ENB Input

When the laser drive current is controlled by the DATA input,

the M66515’s internal current source is maintained turned on.

In contrast, the control by ENB is turning on and off at the cur-

rent source. If ENB = “L” the current source turns on; if ENB =

“H” off.

When ENB = “H” the C

H

pin is compulsorily fixed to “L” in or-

der to discharge the capacitor connected to the C

H

pin.

4. Internal Reset Function

The M66515 has a reset circuit built in for the protection of

laser from an excessive current flowing at the moment of

power on. The internal current source goes off in the range

Vcc < 3.5V (typ.), and the C

H

pin is compulsorily fixed to “L” at

the same time.

5. RO Pin

A load resistor for laser drive current is connected to the RO

pin, through which a current almost equal to I

SW

flows in

(when DATA = “H”). The load resistor is connected between

the RO pin and Vcc to reduce power dissipated in the IC.

Due to reasons related to the operation of circuits, the voltage

at this pin should be 2.5V or higher.

Consequently, the maximum resistance, RO

(max.)

, of load re-

sistor RO is:

Vcc

(min.)

–2.5 [V]

I

SW(max.)

[A]

RO

(max.)

[

] =

where I

SW(max.)

is the maximum of I

SW

. If, for example,

Vcc

(min.)

= 4.75V and I

SW(max.)

=120mA, RO

(max.)

=18.8

.

Accordingly, if the resistance of R

S

is selected so as to gain

maximum I

SW

of 120mA, RO should be 18.8

at the maxi-

mum.

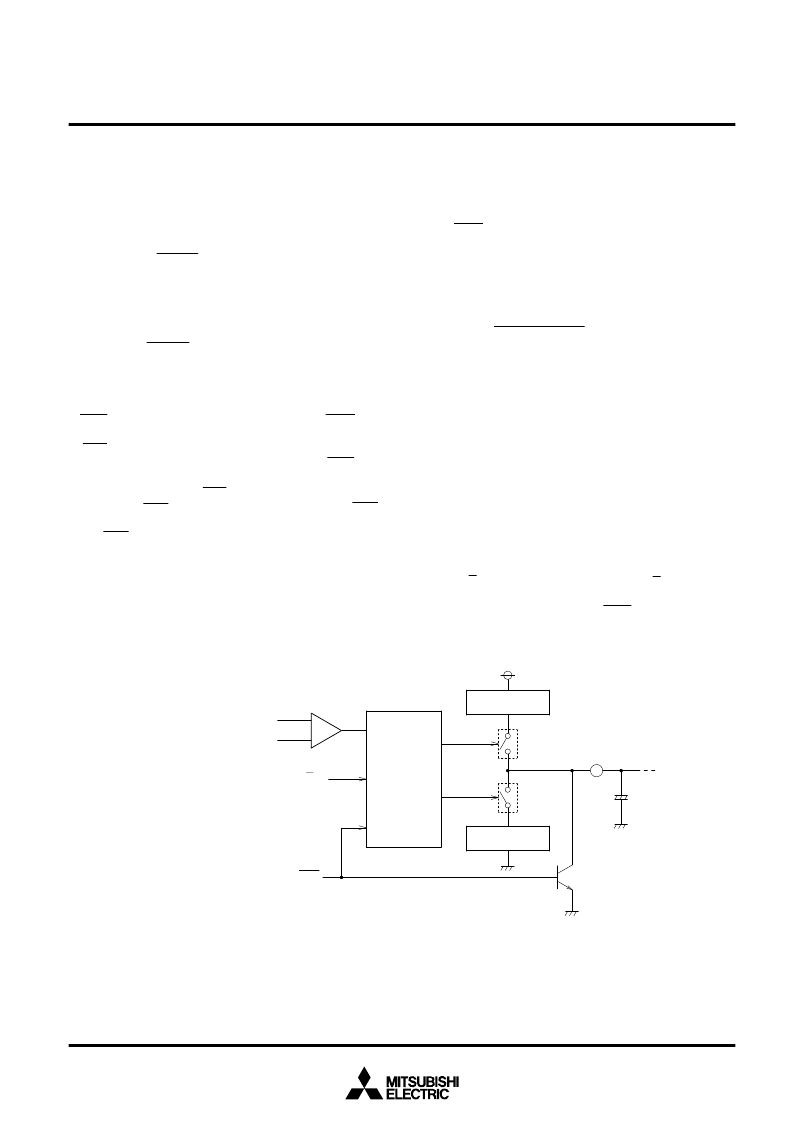

6. Sample-Hold Circuit

(1) Circuit Operation Overview

The following is an overview of the operation of the sample-

hold circuit contained in the M66515.

The PD current generated by LD illumination flows through

the resistor connected between 1RM and 2RM, thereby gen-

erating a potential difference (V

M

). V

M

is compared with the

voltage applied to the Vr pin. If V

M

< Vr, a constant current is

sourced through the C

H

pin so that the external capacitor is

charged. If V

M

> Vr, a constant current sinks through the C

H

pin to discharge the external capacitor.This operation occurs

when the S/H input is “L” (sample). When the S/H input is “H,”

the C

H

pin is maintained at high impedance state (hold), irre-

spective of the state of V

M

, Vr, and DATA input.

Reference voltage input

Potential difference on resistor RM

V

r

V

M

Comparator

+

Control

circuit

S/H

Sample-hold

control input

ENB

SW1

SW2

C

H

T

r1

Externat capacitor

Constant current

source for charging

Constant current

source for discharging

Output

Conceptual Diagram : Sample-Hold circuit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M66515 | LASER-DIODE DRIVER/CONTROLLER |

| M66700P | DUAL HIGH-SPEED CCD CLOCK DRIVER |

| M66700WP | DUAL HIGH-SPEED CCD CLOCK DRIVER |

| M66701P | DUAL HIGH-SPEED CCD CLOCK DRIVER |

| M66851FP | SRAM TYPE FIFO MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M66515FP#TC2J | 功能描述:IC LASR CTRLR 40MBPS 5.25V 20SOP RoHS:是 類別:集成電路 (IC) >> PMIC - 激光驅(qū)動(dòng)器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:60 系列:- 類型:激光二極管驅(qū)動(dòng)器 數(shù)據(jù)速率:- 通道數(shù):4 電源電壓:3.3V 電流 - 電源:- 電流 - 調(diào)制:- 電流 - 偏置:- 工作溫度:0°C ~ 70°C 封裝/外殼:40-TQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:40-TQFN EP 包裝:托盤 安裝類型:表面貼裝 |

| M66515FP(#TC2J) | 制造商:Renesas Electronics Corporation 功能描述: |

| M66516FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:LASER-DIODE DRIVER/CONTROLLER |

| M6657 | 制造商:Tamura Corporation of America 功能描述: |

| M6658 | 制造商:Tamura Corporation of America 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。