- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224185 > M95256-WDW3T/A (STMICROELECTRONICS) 32K X 8 SPI BUS SERIAL EEPROM, PDSO8 PDF資料下載

參數(shù)資料

| 型號(hào): | M95256-WDW3T/A |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 32K X 8 SPI BUS SERIAL EEPROM, PDSO8 |

| 封裝: | 0.169 INCH, TSSOP-8 |

| 文件頁數(shù): | 10/43頁 |

| 文件大?。?/td> | 431K |

| 代理商: | M95256-WDW3T/A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

Instructions

M95256, M95256-W, M95256-R

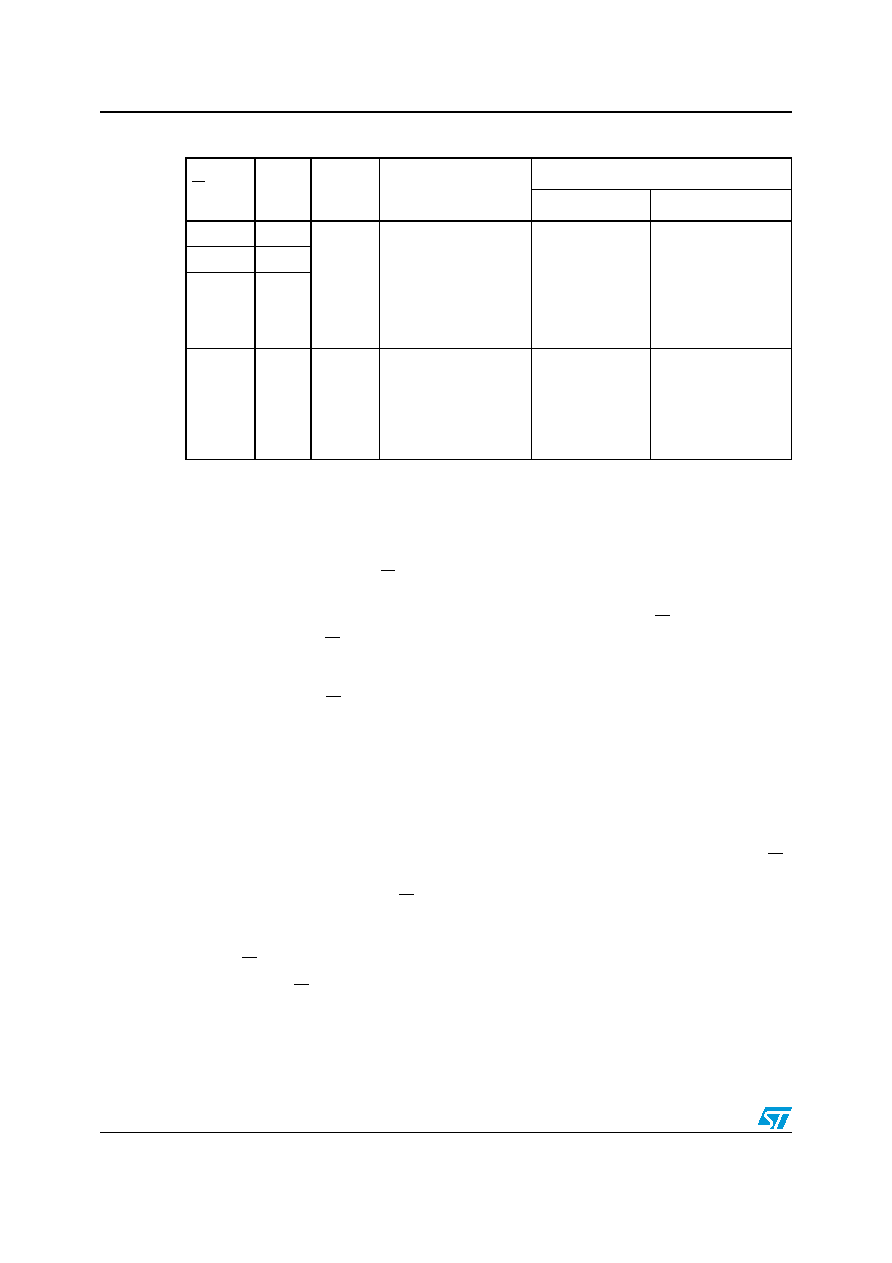

The protection features of the device are summarized in Table 2.

When the Status Register Write Disable (SRWD) bit of the Status Register is 0 (its initial

delivery state), it is possible to write to the Status Register provided that the Write Enable

Latch (WEL) bit has previously been set by a Write Enable (WREN) instruction, regardless

of the whether Write Protect (W) is driven High or Low.

When the Status Register Write Disable (SRWD) bit of the Status Register is set to 1, two

cases need to be considered, depending on the state of Write Protect (W):

●

If Write Protect (W) is driven High, it is possible to write to the Status Register provided

that the Write Enable Latch (WEL) bit has previously been set by a Write Enable

(WREN) instruction.

●

If Write Protect (W) is driven Low, it is not possible to write to the Status Register even

if the Write Enable Latch (WEL) bit has previously been set by a Write Enable (WREN)

instruction. (Attempts to write to the Status Register are rejected, and are not accepted

for execution). As a consequence, all the data bytes in the memory area that are

software protected (SPM) by the Block Protect (BP1, BP0) bits of the Status Register,

are also hardware protected against data modification.

Regardless of the order of the two events, the Hardware Protected Mode (HPM) can be

entered:

●

by setting the Status Register Write Disable (SRWD) bit after driving Write Protect (W)

Low

●

or by driving Write Protect (W) Low after setting the Status Register Write Disable

(SRWD) bit.

The only way to exit the Hardware Protected Mode (HPM) once entered is to pull Write

Protect (W) High.

If Write Protect (W) is permanently tied High, the Hardware Protected Mode (HPM) can

never be activated, and only the Software Protected Mode (SPM), using the Block Protect

(BP1, BP0) bits of the Status Register, can be used.

Table 5.

Protection Modes

W Signal

SRWD

Bit

Mode

Write Protection of the

Status Register

Memory Content

Protected Area(1)

1.

As defined by the values in the Block Protect (BP1, BP0) bits of the Status Register, as shown in Table 5.

Unprotected Area(1)

10

Software

Protected

(SPM)

Status Register is

Writable (if the WREN

instruction has set the

WEL bit)

The values in the BP1

and BP0 bits can be

changed

Write Protected

Ready to accept Write

instructions

00

11

01

Hardware

Protected

(HPM)

Status Register is

Hardware write

protected

The values in the BP1

and BP0 bits cannot be

changed

Write Protected

Ready to accept Write

instructions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M95256-RDW6TG | 32K X 8 SPI BUS SERIAL EEPROM, PDSO8 |

| MA-306-29.4912M-K0 | QUARTZ CRYSTAL RESONATOR, 29.4912 MHz |

| MA04206 | 2-PORT SAW RESONATOR, 433.92 MHz |

| MA05199 | 1-PORT SAW RESONATOR, 434.42 MHz |

| MA1050 | 1 A SWITCHING REGULATOR, 200 kHz SWITCHING FREQ-MAX, SIP7 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M95256WDW3TG | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit serial SPI bus EEPROM with high-speed clock |

| M95256-WDW3TG | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256Kbit and 128Kbit Serial SPI Bus EEPROM With High Speed Clock |

| M95256-WDW3TG/A | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit Serial SPI bus EEPROM with high speed clock |

| M95256-WDW3TG/K | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit serial SPI bus EEPROM with high-speed clock |

| M95256-WDW3TG/V | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit Serial SPI bus EEPROM with high speed clock |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。