- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180472 > MACH131SP-12YI (LATTICE SEMICONDUCTOR CORP) High-Performance EE CMOS Programmable Logic PDF資料下載

參數(shù)資料

| 型號: | MACH131SP-12YI |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | High-Performance EE CMOS Programmable Logic |

| 中文描述: | EE PLD, 10 ns, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁數(shù): | 44/48頁 |

| 文件大小: | 1136K |

| 代理商: | MACH131SP-12YI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁

MACH 1 & 2 Families

5

Each PAL block consists of the following elements:

x

Product-term array

x

Logic Allocator

x

Macrocells

x

I/O cells

Each PAL block additionally contains an asynchronous reset product term and an asynchronous

preset product term. This allows the ip-ops within a single PAL block to be initialized as a bank.

There are also output enable product terms that provide tri-state control for the I/O cells.

Product-Term Array

The product-term array consists of a number of product terms that form the basis of the logic being

implemented. The inputs to the AND gates come from the switch matrix (Table 4), and are

provided in both true and complement forms for efcient logic implementation.

Because the number of product terms available for a given function is not xed, the full sum of

products is not realized in the array. The product terms drive the logic allocator, which allocates

the appropriate number of product terms to generate the function.

Logic Allocator

The logic allocator (Figure 2) is a block within which different product terms are allocated to the

appropriate macrocells in groups of four product terms called “product term clusters”. The

availability and distribution of product term clusters is automatically considered by the software as

it ts functions within the PAL block. The size of the product term clusters has been designed to

provide high utilization of product terms. Complex functions using many product terms are

possible, and when few product terms are used, there will be a minimal number of unused, or

wasted, product terms left over.

The product term clusters do not “wrap” around the logic block. This means that the macrocells

at the ends of the block have fewer product terms available (Tables 5, 6, 7, 8).

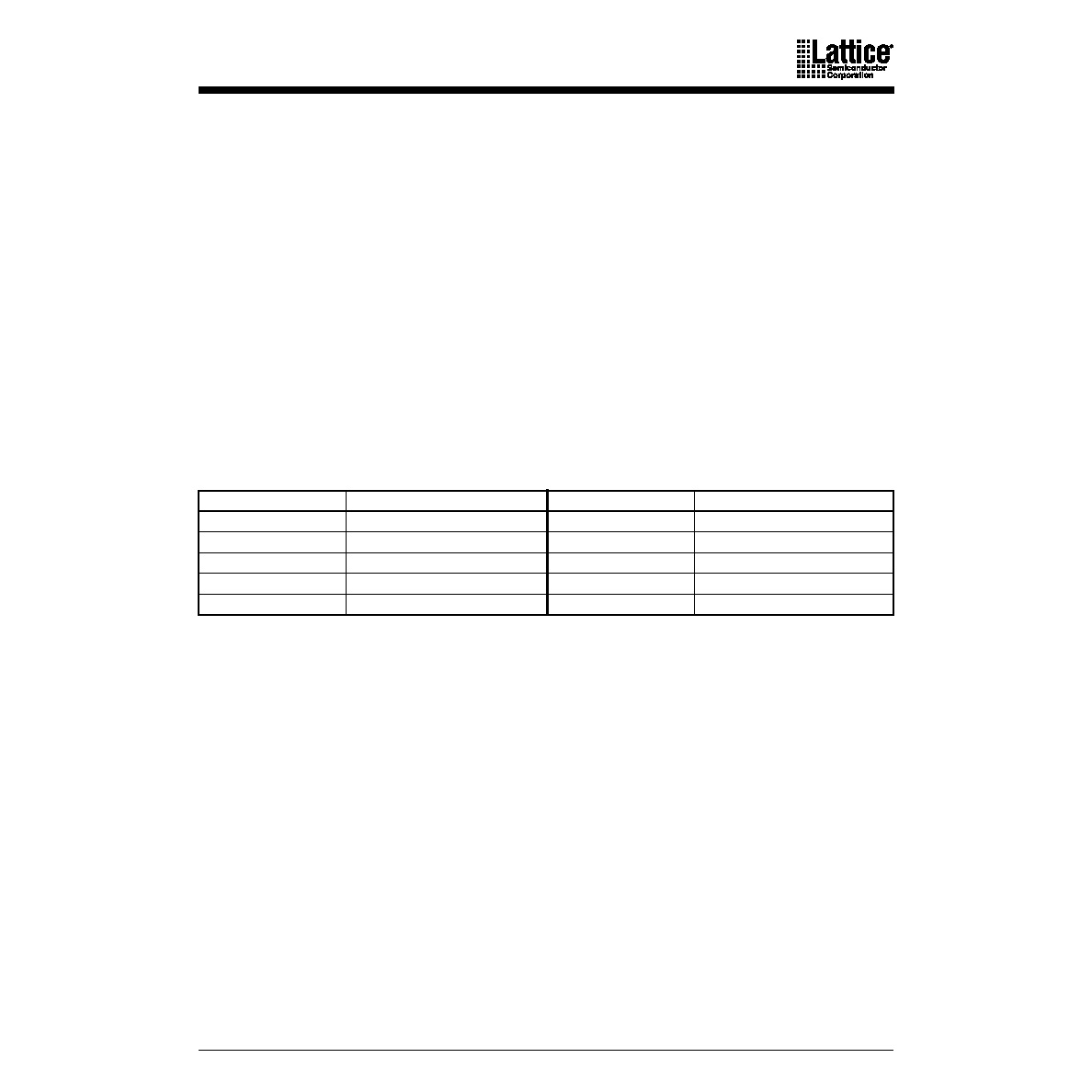

Table 4. PAL Block Inputs

Device

Number of Inputs to PAL Block

Device

Number of Inputs to PAL Block

MACH111

26

MACH211SP

26

MACH111SP

26

MACH221

26

MACH131

26

MACH221SP

26

MACH131SP

26

MACH231

32

MACH211

26

MACH231SP

32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MACH131SP-14YI | High-Performance EE CMOS Programmable Logic |

| MACH131SP-15VC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-5VC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-7VC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-7YI | High-Performance EE CMOS Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MACH131SP-14YI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF EE CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| MACH131SP-15VC | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Lattice Semiconductor Corporation 功能描述: |

| MACH131SP-15YC | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH131SP-18YI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF EE CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| MACH131SP-5VC | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。