- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11587 > MAX3420EECJ+ (Maxim Integrated Products)IC USB PERIPH CONTROLLER 32TQFP PDF資料下載

參數(shù)資料

| 型號: | MAX3420EECJ+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 7/22頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC USB PERIPH CONTROLLER 32TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 250 |

| 控制器類型: | USB 外設(shè)控制器 |

| 接口: | USB/串行 |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 15mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-LQFP |

| 供應(yīng)商設(shè)備封裝: | 32-LQFP(7x7) |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁面: | 1407 (CN2011-ZH PDF) |

| 配用: | MAX3420EEVKIT-2+-ND - EVAL KIT FOR MAX3420E |

In full-duplex mode (FDUPSPI = 1), the MOSI and MISO

pins are separate, and the MISO pin drives only when SS

is low. In this mode, the first eight SCLK edges (after SS =

0) clock the command byte into the MAX3420E on MOSI,

and eight USB status bits are clocked out of the

MAX3420E on MISO. For an SPI write cycle, any bytes

following the command byte are clocked into the

MAX3420E on MOSI, and zeros are clocked out on MISO.

For an SPI read cycle, any bytes following the command

byte are clocked out of the MAX3420E on MISO and the

data on MOSI is ignored. At the conclusion of the SPI

cycle (SS = 1), the MISO output tri-states.

In half-duplex mode, the MOSI pin is a bidirectional pin

and the MISO pin is tri-stated. This saves a pin in the SPI

interface. Because of the shared data pin, this mode

does not offer the eight USB status bits (Figure 5) as the

command byte is clocked into the MAX3420E. The MISO

pin can be left unconnected in half-duplex mode.

SCLK (Serial Clock)

The SPI master provides the MAX3420E SCLK signal to

clock the SPI interface. SCLK has no low-frequency limit,

and can be as high as 26MHz. The MAX3420E changes

its output data (MISO) on the falling edge of SCLK and

samples input data (MOSI) on the rising edge of SCLK.

The MAX3420E ignores SCLK transitions when SS is

high. The inactive level of SCLK may be low or high,

depending on the SPI operating mode (Figure 14).

SS (Slave Select)

The MAX3420E SPI interface is active only when SS is

low. When SS is high, the MAX3420E tri-states the SPI

output pin and resets the internal MAX3420E SPI logic.

If SS goes high before a complete byte is clocked in,

the byte-in-progress is discarded. The SPI master can

terminate an SPI cycle after clocking in the first 8 bits

(the command byte). This feature can be used in a full-

duplex system to retrieve the USB status bits (Figure 5)

without sending or receiving SPI data.

Applications Information

SPI Interface

The MAX3420E operates as an SPI slave device. A reg-

ister access consists of the SPI master first writing an

SPI command byte, followed by reading or writing the

contents of the addressed register (see the

Register

Description section for more details). All SPI transfers

are MSB first. The external SPI master provides a clock

signal to the MAX3420E SCLK input. This clock fre-

quency can be between DC and 26MHz. Bit transfers

occur on the positive edge of SCLK. The MAX3420E

counts bits and divides them into bytes. If fewer than 8

bits are clocked into the MAX3420E when SS goes

high, the MAX3420E discards the partial byte.

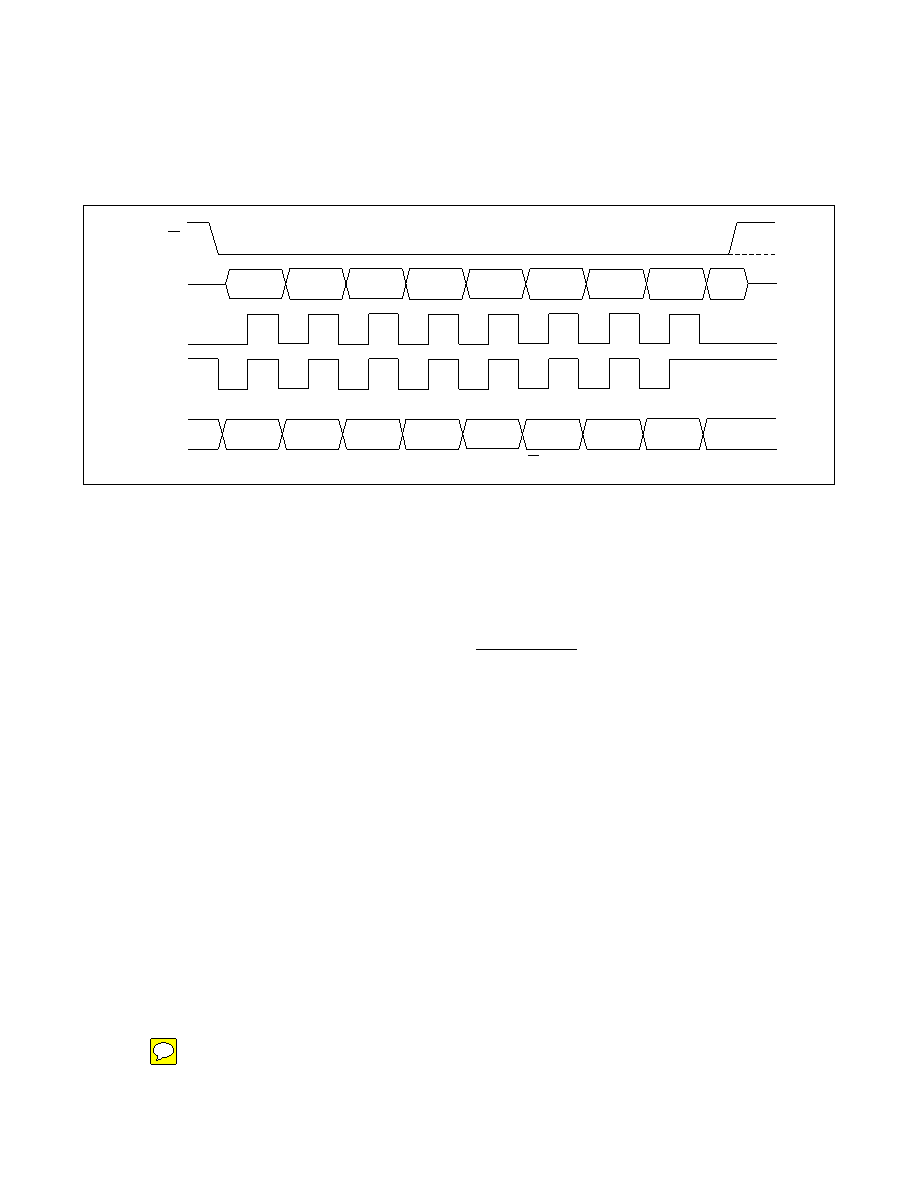

The MAX3420E SPI interface operates without adjust-

ment in either SPI mode (CPOL = 0, CPHA = 0) or

(CPOL = 1, CPHA = 1). No mode bit is required to

select between the two modes since the interface uses

the rising edge of the clock in both modes. The two

clocking modes are illustrated in Figure 14. Note that

the inactive SCLK value is different for the two modes.

Figure 14 illustrates the full-duplex mode, where data is

simultaneously clocked into and out of the MAX3420E.

USB Peripheral Controller

with SPI Interface

SS

MISO

MOSI

SCLK

MODE 0,0

SCLK

MODE 1,1

SPI MODE 0,0 OR 1,1

*MSB OF NEXT BYTE IN BURST MODE (SS REMAINS LOW)

Q7

Q6

Q5

Q4

Q3

D7

D6

D5

D4

D3

D2

D1

D0

*

Q2

Q1

Q0

*

Figure 14. SPI Clocking Modes

MAX3420E

Maxim Integrated

15

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX3420EETG+ | IC USB PERIPH CONTROLLER 24TQFN |

| PIC12F629-E/SN | IC MCU CMOS 8BIT 1K FLASH 8-SOIC |

| PIC12LC508A-04I/MF | IC MCU OTP 512X12 LV 8DFN |

| PIC16F631-E/P | IC PIC MCU FLASH 1KX14 20DIP |

| PIC16C620A-04I/SO | IC MCU OTP 512X14 COMP 18SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3420EECJ/V+ | 功能描述:外圍驅(qū)動器與原件 - PCI USB Peripheral Controller with SPI Interface RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3420EECJ/V+T | 功能描述:外圍驅(qū)動器與原件 - PCI USB Peripheral Controller with SPI Interface RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3420EECJ+ | 功能描述:外圍驅(qū)動器與原件 - PCI USB Peripheral Controller w/SPI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3420EECJ+T | 功能描述:外圍驅(qū)動器與原件 - PCI USB Peripheral Controller w/SPI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3420EECJ-T | 功能描述:外圍驅(qū)動器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。