- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9529 > MAX3991UTG+ (Maxim Integrated Products)IC DATA RECOVERY W/AMP 24-TQFN PDF資料下載

參數(shù)資料

| 型號(hào): | MAX3991UTG+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 12/12頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC DATA RECOVERY W/AMP 24-TQFN |

| 標(biāo)準(zhǔn)包裝: | 75 |

| 類型: | 時(shí)鐘和數(shù)據(jù)恢復(fù)(CDR) |

| PLL: | 是 |

| 主要目的: | SONET/SDH.XFP 光學(xué)接收器 |

| 輸入: | CML |

| 輸出: | CML |

| 電路數(shù): | 1 |

| 比率 - 輸入:輸出: | 1:2 |

| 差分 - 輸入:輸出: | 是/是 |

| 頻率 - 最大: | 693.5MHz |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 24-WFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 24-TQFN-EP(4x4) |

| 包裝: | 管件 |

PLL Retimer

The integrated PLL recovers a synchronous clock,

which is used to retime the input data. Connect a

0.047F capacitor between CFIL and VCC to provide

PLL dampening. The external reference connected to

REFCLK aids in frequency acquisition. Because the ref-

erence clock is only used for frequency acquisition, a

low-quality reference clock can be used with no penalty

in performance. The reference clock should be within

±100ppm of the bit rate divided by 16 or 64.

Loss-of-Lock Monitor

The LOL output indicates that the frequency difference

between the recovered clock and the reference clock is

excessive. LOL may assert due to excessive jitter at the

data input, incorrect frequency, or loss of input data.

The LOL detector monitors the frequency difference

between the recovered clock and the reference clock.

The LOL output is asserted high when the frequency

difference exceeds 650ppm.

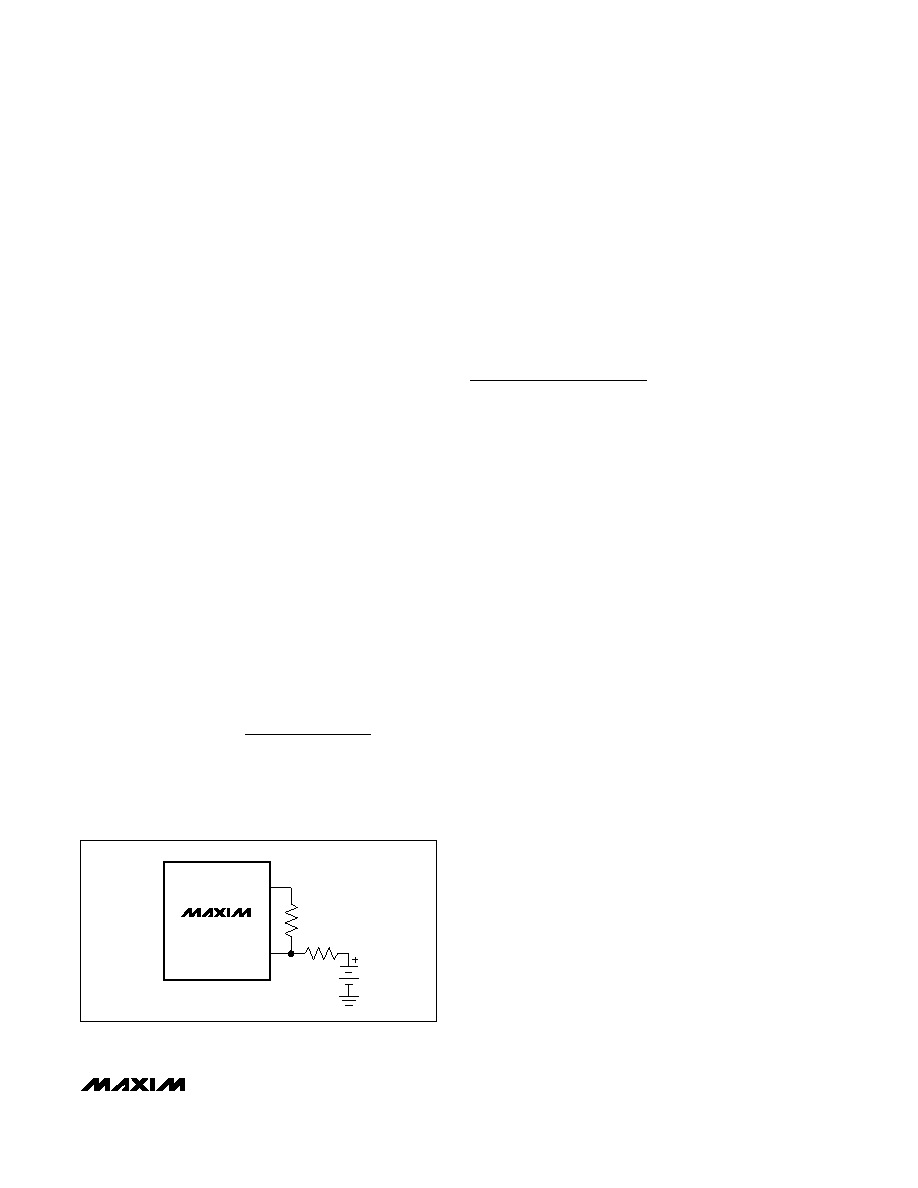

Loss-of-Signal Monitor

The LOS output indicates low, receive-signal power.

The LOS output is asserted high when the input signal

is below the threshold set by VTH.

VTH = 10 x VLOS_ASSERT(mVP-P) (typ)

The hysteresis value of the LOS detector is internally

fixed at 1.5. Hysteresis values above 1.5 can be

achieved using external resistors as shown in Figure 4.

The new hysteresis value is:

Resistor R2 is selected to prevent loading of the LOS

pin. A value of >40k

is recommended. Refer to appli-

cations note HFDN 34-0.

Reference Clock Input

The REFCLK inputs are internally terminated and self-

biased to allow AC-coupling. The input impedance is

100

single-ended (200 differential). The REFCLK

inputs of the MAX3991 and MAX3992 should be con-

nected close together in parallel. The impedance look-

ing into the parallel combination is 100

differential.

This allows both the MAX3991 and MAX3992 to easily

interface with one reference clock without using addi-

tional components. See Figure 5.

Design Procedure

Modes of Operation

The MAX3991 has a standby mode, jitter test mode,

and squelch mode in addition to its normal operating

mode. Standby is used to conserve power. In the

standby mode, the power consumption of the MAX3991

falls below 40% of the normal-operation power con-

sumption. The jitter test mode enables the SCLK out-

puts to clock a BERT when testing jitter generation,

jitter transfer, and jitter tolerance. In the squelch mode,

the SDO± outputs are held static at VCC. The FCTL1

and FCTL2 TTL inputs are used to select the mode of

operation as shown in Table 3.

Serial Data Rate and

Reference Clock Frequency

Input Configuration

The SDI

± inputs of the MAX3991 are current-mode

logic (CML) compatible. The inputs have internal 50

terminations for minimum external components. See

Figure 6 for the input structure. AC-coupling is recom-

mended. The common-mode levels of DC-coupled

parts must be matched. For additional information on

logic interfacing, refer to Maxim Application Note HFAN

1.0: Introduction to LVDS, PECL, and CML.

Output Configuration

The MAX3991 uses CML for its high-speed digital out-

puts (SDO

± and SCLKO±). The configuration of the out-

put circuit includes internal 50

back terminations to

VCC. See Figure 7 for the output structure. CML outputs

may be terminated by 50

to VCC, or by 100 differen-

tial impedance. The relation of the output polarity to input

can be reversed using the POL pin (see Figure 8).

For additional information on logic interfacing, refer to

Maxim Application Note HFAN 1.0: Introduction to LVDS,

PECL, and CML.

H1

3R

R

0R

R

REF

ysteresis

V

=×

×+

×

×+

×

.

5

12

21

2

MAX3991

10Gbps Clock and Data Recovery

with Limiting Amplifier

_______________________________________________________________________________________

9

Figure 4. Added Hysteresis Circuit

MAX3992

LOS

VTH

R2

R1

VREF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS276S+ | IC TXRX LOW POWER RS-232 8-SOIC |

| V28A8M200BF2 | CONVERTER MOD DC/DC 8V 200W |

| DS275S+T&R | IC TXRX LINE-PWR RS232 8-SOIC |

| V28A8M200BF | CONVERTER MOD DC/DC 8V 200W |

| DS275S+ | IC TXRX LINE-PWR RS232 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3991UTG+ | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 10Gbps Clock & Data Recovery RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

| MAX3991UTG+T | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 10Gbps Clock & Data Recovery RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

| MAX3992UTG+ | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 10Gbps Clock & Data Recovery RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

| MAX3992UTG+T | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 10Gbps Clock & Data Recovery RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

| MAX3996CGP | 功能描述:激光驅(qū)動(dòng)器 3-5.5V 2.5Gbps VCSEL & Laser Driver RoHS:否 制造商:Micrel 數(shù)據(jù)速率:4.25 Gbps 工作電源電壓:3 V to 3.6 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-16 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。