- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383541 > MAX9242_07 (Maxim Integrated Products, Inc.) 21-Bit Deserializers with Programmable Spread Spectrum and DC Balance PDF資料下載

參數(shù)資料

| 型號(hào): | MAX9242_07 |

| 廠商: | Maxim Integrated Products, Inc. |

| 英文描述: | 21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| 中文描述: | 21與可編程擴(kuò)頻和直流平衡位解串器 |

| 文件頁(yè)數(shù): | 18/22頁(yè) |

| 文件大小: | 306K |

| 代理商: | MAX9242_07 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

M

21-Bit Deserializers with Programmable

Spread Spectrum and DC Balance

18

______________________________________________________________________________________

The capacitor value decreases for a higher frequency

parallel clock and for higher levels of droop and jitter.

Use high-frequency, surface-mount ceramic capacitors.

Equation 1 altered for four series capacitors (Figure 20) is:

C = -(4 x t

B

x DSV) / (ln (1 - D) x (R

T

+ R

O

)) (Eq 3)

Fail-Safe

The MAX9242/MAX9244/MAX9246/MAX9254 have fail-

safe LVDS inputs in non-DC-balanced mode (Figure 1).

Fail-safe drives the outputs low when the corresponding

LVDS input is open, undriven and shorted, or undriven

and parallel terminated. The fail-safe on the LVDS clock

input drives all outputs low when power is stable. Fail-

safe does not operate in DC-balanced mode.

Input Bias and Frequency Detection

In DC-balanced mode, the inverting and noninverting

LVDS inputs are internally connected to +1.2V through

42k

Ω

(min) to provide biasing for AC-coupling (Figure 1).

To prevent switching due to noise when the clock input

is not driven, bias the clock inputs (RxCLKIN+,

RxCLKIN-) to differential +15mV by connecting a 10k

Ω

±1% pullup resistor between the noninverting input and

LVDSV

CC

, and a 10k

Ω

±1% pulldown resistor between

the inverting input and ground. These bias resistors,

along with the 100

Ω

±1% tolerant termination resistor,

provide +15mV of differential input. The +15mV bias

causes some small degradation of RSKM proportional to

the slew rate of the clock input. For example, if the clock

transitions 250mV in 500ps, the slew rate of 0.5mV/ps

reduces RSKM by 30ps.

Unused LVDS Data Inputs

In non-DC-balanced mode, leave unused LVDS data

inputs open. In non-DC-balanced mode, the input fail-

safe circuit drives the corresponding outputs low, and no

pullup or pulldown resistors are needed. In DC-balanced

mode, at each unused LVDS data input, pull the inverting

input up to LVDSV

CC

using a 10k

Ω

resistor, and pull the

noninverting input down to ground using a 10k

Ω

resistor.

Do not connect a termination resistor. The pullup and

pulldown resistors drive the corresponding outputs low

and prevent switching due to noise.

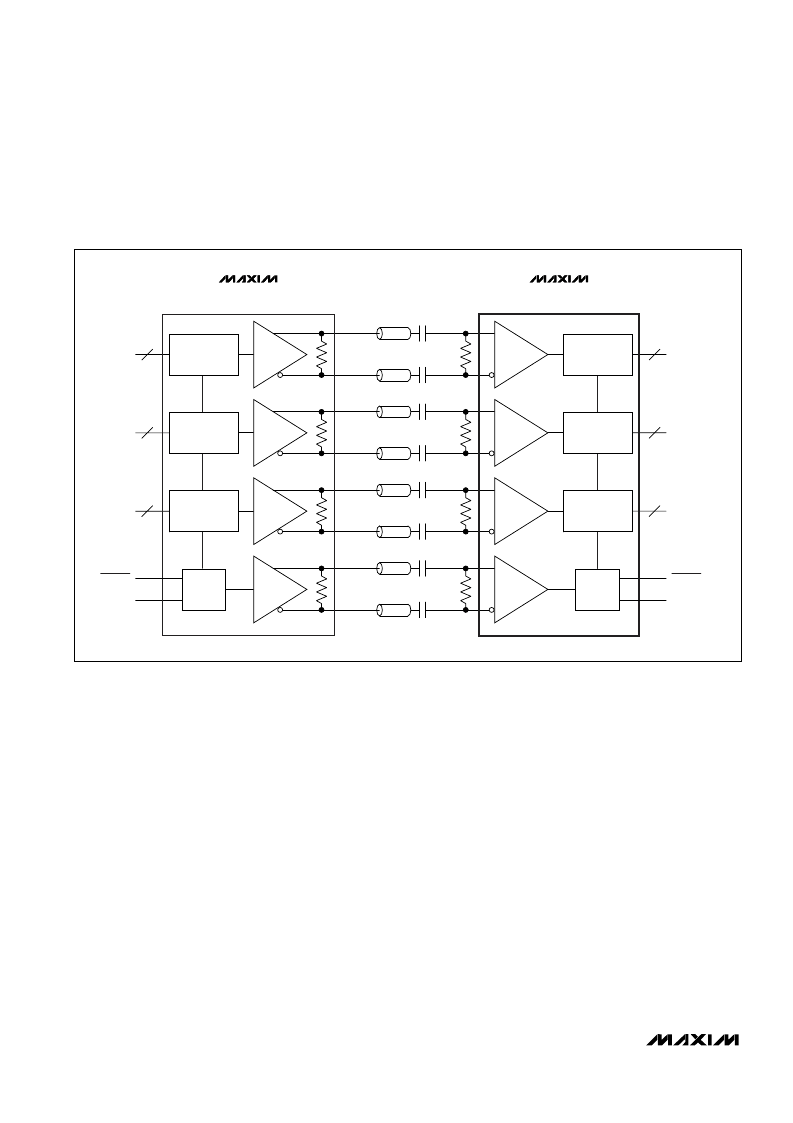

(7 + 2):1

7

7

100

Ω

(7 + 2):1

7

7

100

Ω

(7 + 2):1

1:(9 - 2)

+ FIFO

1:(9 - 2)

+ FIFO

1:(9 - 2)

+ FIFO

7

7

100

Ω

PLL

100

Ω

MAX9209/MAX9213

MAX9242/MAX9244/MAX9246/MAX9254

TxOUT

TxCLK OUT

RxIN

RxCLK IN

21:3 SERIALIZER

3:21 DESERIALIZER

PWRDWN

RxCLK OUT

RxOUT

PWRDWN

TxCLK IN

TxIN

HIGH-FREQUENCY, CERAMIC

SURFACE-MOUNT CAPACITORS

CAN ALSO BE PLACED AT THE

SERIALIZER INSTEAD OF THE DESERIALIZER.

PLL1 +

SSPLL

R

O

R

T

Figure 19. Two Capacitors per Link, AC-Coupled, DC-Balanced Mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX9242EUM | 21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| MAX9242GUM | 21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| MAX9244GUM | 21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| MAX9246EUM | 21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| MAX9246GUM | 21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9242EUM | 功能描述:LVDS 接口集成電路 RoHS:否 制造商:Texas Instruments 激勵(lì)器數(shù)量:4 接收機(jī)數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| MAX9242EUM/V+ | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9242EUM/V+T | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9242EUM+ | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9242EUM+D | 制造商:Maxim Integrated Products 功能描述:21-BIT DC-BALANCED LVDS DESERIALIZERS WITH SPREAD SPECTRUM - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。