- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11685 > MAX9259GCB/V+ (Maxim Integrated Products)IC SERIALIZER GMSL 64TQFP PDF資料下載

參數(shù)資料

| 型號: | MAX9259GCB/V+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 22/51頁 |

| 文件大小: | 0K |

| 描述: | IC SERIALIZER GMSL 64TQFP |

| 標準包裝: | 160 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

Gigabit Multimedia Serial Link with Spread

Spectrum and Full-Duplex Control Channel

MAX9259/MAX9260

______________________________________________________________________________________ 29

Choose MCLKDIV values so that fMCLK is not greater

than 60MHz. MCLK frequencies derived from PCLK_

(MCLKSRC = 0) are not affected by spread-spectrum

settings in the deserializer (MAX9260). Enabling spread

spectrum in the serializer (MAX9259), however, intro-

duces spread spectrum into MCLK. Spread-spectrum

settings of either device do not affect MCLK frequencies

derived from the internal oscillator. The internal oscilla-

tor frequency ranges from 100MHz to 150MHz over all

process corners and operating conditions.

Control-Channel and Register Programming

The FC uses the control link to send and receive control

data over the STP link simultaneously with the high-speed

data. Configuring the CDS pin allows the FC to control the

link from either the MAX9259 or the MAX9260 side to sup-

port video-display or image-sensing applications.

The control link between the FC and the MAX9259 or

MAX9260 runs in base mode or bypass mode accord-

ing to the mode selection (MS) input of the device con-

nected to the FC. Base mode is a half-duplex control link

and the bypass mode is a full-duplex control link. In base

mode, the FC is the host and accesses the registers of

both the MAX9259 and MAX9260 from either side of the

link by using the GMSL UART protocol. The FC can also

program the peripherals on the remote side by sending

the UART packets to the MAX9259 or MAX9260, with

UART packets converted to I2C by the device on the

remote side of the link (MAX9260 for LCD or MAX9259

for image-sensing applications). The FC communicates

with a UART peripheral in base mode (through INTTYPE

register settings) using the half-duplex default GMSL

UART protocol of the MAX9259 and MAX9260. The

device addresses of the MAX9259 and MAX9260 in the

base mode are programmable. The default values are

0x80 and 0x90, respectively.

In base mode, when the peripheral interface uses I2C

(default), the MAX9259/MAX9260 only convert packets

that have device addresses different from those of the

MAX9259 or MAX9260 to I2C. The converted I2C bit rate

is the same as the original UART bit rate.

In bypass mode, the FC bypasses the MAX9259/

MAX9260 and communicates with the peripherals direct-

ly using its own defined UART protocol. The FC cannot

access the MAX9259/MAX9260’s registers in this mode.

Peripherals accessed through the forward control chan-

nel using the UART interface need to handle at least one

PCLK_ period of jitter due to the asynchronous sampling

of the UART signal by PCLK_.

The MAX9259 embeds control signals going to the

MAX9260 in the high-speed forward link. Do not send

a low value longer than 100Fs in either base or bypass

mode. The MAX9260 uses a proprietary differential line

coding to send signals back towards the MAX9259. The

speed of the control link ranges from 100kbps to 1Mbps

in both directions. The MAX9259/MAX9260 automatically

detect the control-channel bit rate in base mode. Packet

bit rates can vary up to 3.5x from the previous bit rate

(see the Changing the Data Frequency section). Figure

24 shows the UART protocol for writing and reading in

base mode between the FC and the MAX9259/MAX9260.

Figure 25 shows the UART data format. Even parity is

used. Figures 26 and 27 detail the formats of the SYNC

byte (0x79) and ACK byte (0xC3). The FC and the con-

nected slave chip generate the SYNC byte and ACK

byte, respectively. Certain events such as device wake-

up and interrupt generate signals on the control path and

should be ignored by the FC. All data written to the inter-

nal registers do not take affect until after the acknowl-

edge byte is sent. This allows the FC to verify that write

commands are processed without error, even if the result

of the write command directly affects the serial link. The

slave uses the SYNC byte to synchronize with the host

UART data rate automatically. If the INT or MS inputs of

the MAX9260 toggles while there is control-channel com-

munication, the control-channel communication can be

corrupted. In the event of a missed acknowledge, the FC

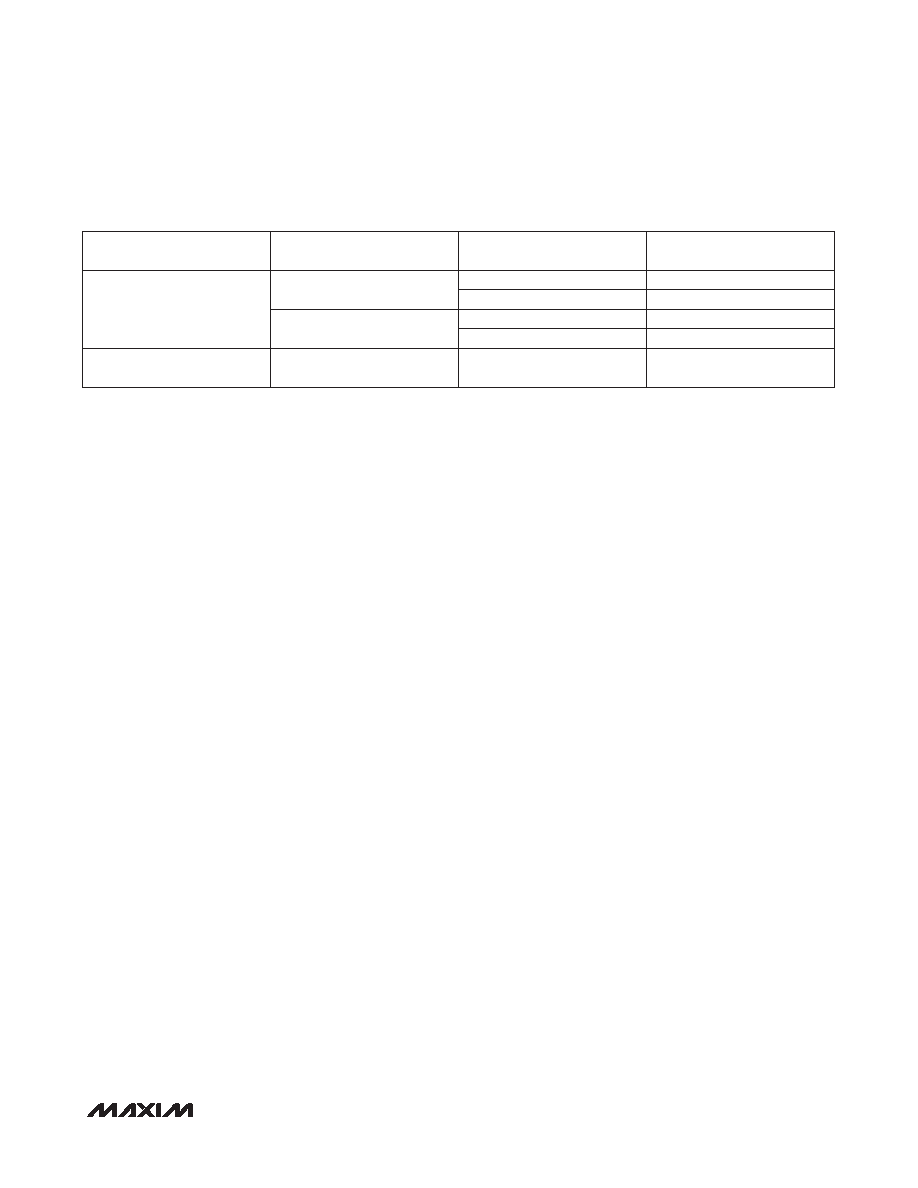

Table 5. MAX9260 fSRC Settings

MCLKSRC SETTING

(REGISTER 0x12, D7)

DATA-RATE SETTING

BIT-WIDTH SETTING

MCLK SOURCE

FREQUENCY (fSRC)

0

High speed

24-bit mode

3 x fPCLKOUT

32-bit mode

4 x fPCLKOUT

Low speed

24-bit mode

6 x fPCLKOUT

32-bit mode

8 x fPCLKOUT

1

—

Internal oscillator

(120MHz typ)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX9247GCM+ | IC SERIALIZER LVDS 48-LQFP |

| VI-J2K-IY-F2 | CONVERTER MOD DC/DC 40V 50W |

| MAX9248ECM/V+T | IC DESERIALIZER LVDS 48-LQFP |

| MAX9248ECM+T | IC DESERIALIZER LVDS 48-TQFP |

| VI-J2K-IY-F1 | CONVERTER MOD DC/DC 40V 50W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9259GTN/V+ | 制造商:Maxim Integrated Products 功能描述:GIGABIT MULTIMEDIA SERIAL LINK WITH SPREAD SPECTRUM AND FULL - Rail/Tube |

| MAX9259GTN/V+GG6 | 制造商:Maxim Integrated Products 功能描述:IC SERIALIZER GMSL |

| MAX9259GTN/V+T | 制造商:Maxim Integrated Products 功能描述: |

| MAX9259GTN/V+TGG6 | 制造商:Maxim Integrated Products 功能描述:IC SERIALIZER GMSL |

| MAX9260EVKIT+ | 功能描述:界面開發(fā)工具 MAX9260 Eval Kit RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。