- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11685 > MAX9259GCB/V+ (Maxim Integrated Products)IC SERIALIZER GMSL 64TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | MAX9259GCB/V+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 4/51頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC SERIALIZER GMSL 64TQFP |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)

Gigabit Multimedia Serial Link with Spread

Spectrum and Full-Duplex Control Channel

MAX9259/MAX9260

12 _____________________________________________________________________________________

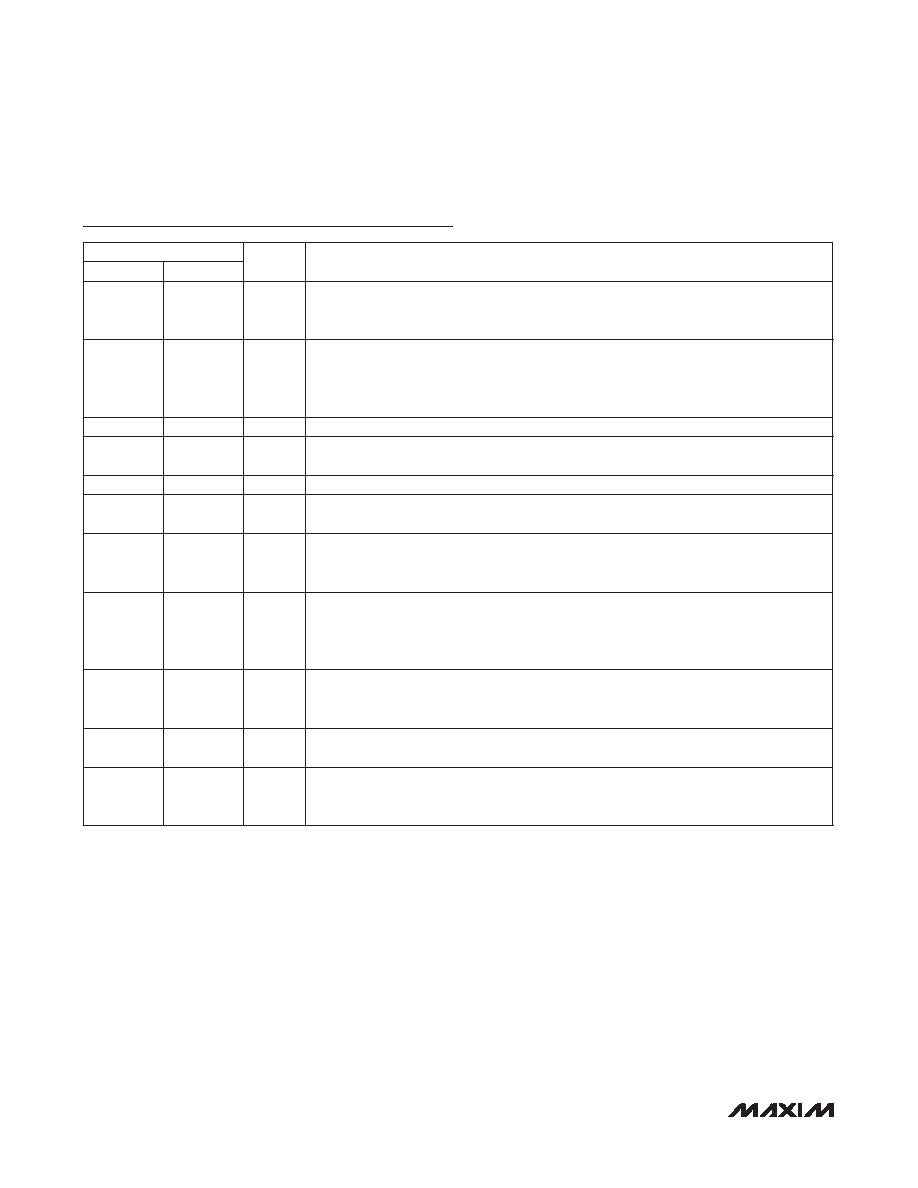

MAX9259 Pin Description (continued)

PIN

NAME

FUNCTION

TQFP

TQFN

36

31

TX/SCL

Transmit/Serial Clock. UART transmit or I2C serial-clock output with internal 30kI

pullup to IOVDD. In UART mode, TX/SCL is the Tx output of the MAX9259’s UART. In I2C

mode, TX/SCL is the SCL output of the MAX9259’s I2C master.

37

32

SSEN

Spread-Spectrum Enable. Serial link spread-spectrum enable input requires external

pulldown or pullup resistors. The state of SSEN latches upon power-up or when resuming

from power-down mode (PWDN = low). Set SSEN = high for Q0.5% spread spectrum on

the serial link. Set SSEN = low to use the serial link without spread spectrum.

38

33

LMN1

Line-Fault Monitor Input 1 (see Figure 3 for details)

40, 41

34, 35

OUT-,

OUT+

Differential CML Output

-/+. Differential outputs of the serial link.

43

37

LMN0

Line-Fault Monitor Input 0 (see Figure 3 for details)

44

38

LFLT

Line Fault. Active-low open-drain line-fault output with a 60kI internal pullup resistor.

LFLT = low indicates a line fault. LFLT is high impedance when PWDN = low.

45

39

INT

Interrupt Output to Indicate Remote Side Requests. INT = low upon power-up and when

PWDN = low. A transition on the INT input of the MAX9260 toggles the MAX9259’s INT

output.

46

40

DRS

Data-Rate Select. Data-rate range-selection input requires external pulldown or pullup

resistors. Set DRS = high for parallel input data rates of 8.33MHz to 16.66MHz (24-bit

mode) or 6.25MHz to 12.5MHz (32-bit mode). Set DRS = low for parallel input data rates

of 16.66MHz to 104MHz (24-bit mode) or 12.5MHz to 78MHz (32-bit mode).

47

41

ES

Edge Select. PCLKIN trigger edge-selection input requires external pulldown or pullup

resistors. Set ES = low to trigger on the rising edge of PCLKIN. Set ES = high to trigger on

the falling edge of PCLKIN.

48

42

BWS

Bus-Width Select. Parallel input bus-width selection input requires external pulldown or

pullup resistors. Set BWS = low for 24-bit bus mode. Set BWS = high for 32-bit bus mode.

—

EP

Exposed Pad. EP internally connected to AGND (TQFP package) or AGND and GND

(TQFN package). MUST externally connect EP to the AGND plane to maximize thermal

and electrical performance.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX9247GCM+ | IC SERIALIZER LVDS 48-LQFP |

| VI-J2K-IY-F2 | CONVERTER MOD DC/DC 40V 50W |

| MAX9248ECM/V+T | IC DESERIALIZER LVDS 48-LQFP |

| MAX9248ECM+T | IC DESERIALIZER LVDS 48-TQFP |

| VI-J2K-IY-F1 | CONVERTER MOD DC/DC 40V 50W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9259GTN/V+ | 制造商:Maxim Integrated Products 功能描述:GIGABIT MULTIMEDIA SERIAL LINK WITH SPREAD SPECTRUM AND FULL - Rail/Tube |

| MAX9259GTN/V+GG6 | 制造商:Maxim Integrated Products 功能描述:IC SERIALIZER GMSL |

| MAX9259GTN/V+T | 制造商:Maxim Integrated Products 功能描述: |

| MAX9259GTN/V+TGG6 | 制造商:Maxim Integrated Products 功能描述:IC SERIALIZER GMSL |

| MAX9260EVKIT+ | 功能描述:界面開發(fā)工具 MAX9260 Eval Kit RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。