- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1946 > MAX9260GCB/V+ (Maxim Integrated Products)IC DESERIALIZER GMSL 64TQFP PDF資料下載

參數(shù)資料

| 型號: | MAX9260GCB/V+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 5/51頁 |

| 文件大小: | 0K |

| 描述: | IC DESERIALIZER GMSL 64TQFP |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 系列: | * |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

Gigabit Multimedia Serial Link with Spread

Spectrum and Full-Duplex Control Channel

MAX9259/MAX9260

______________________________________________________________________________________ 13

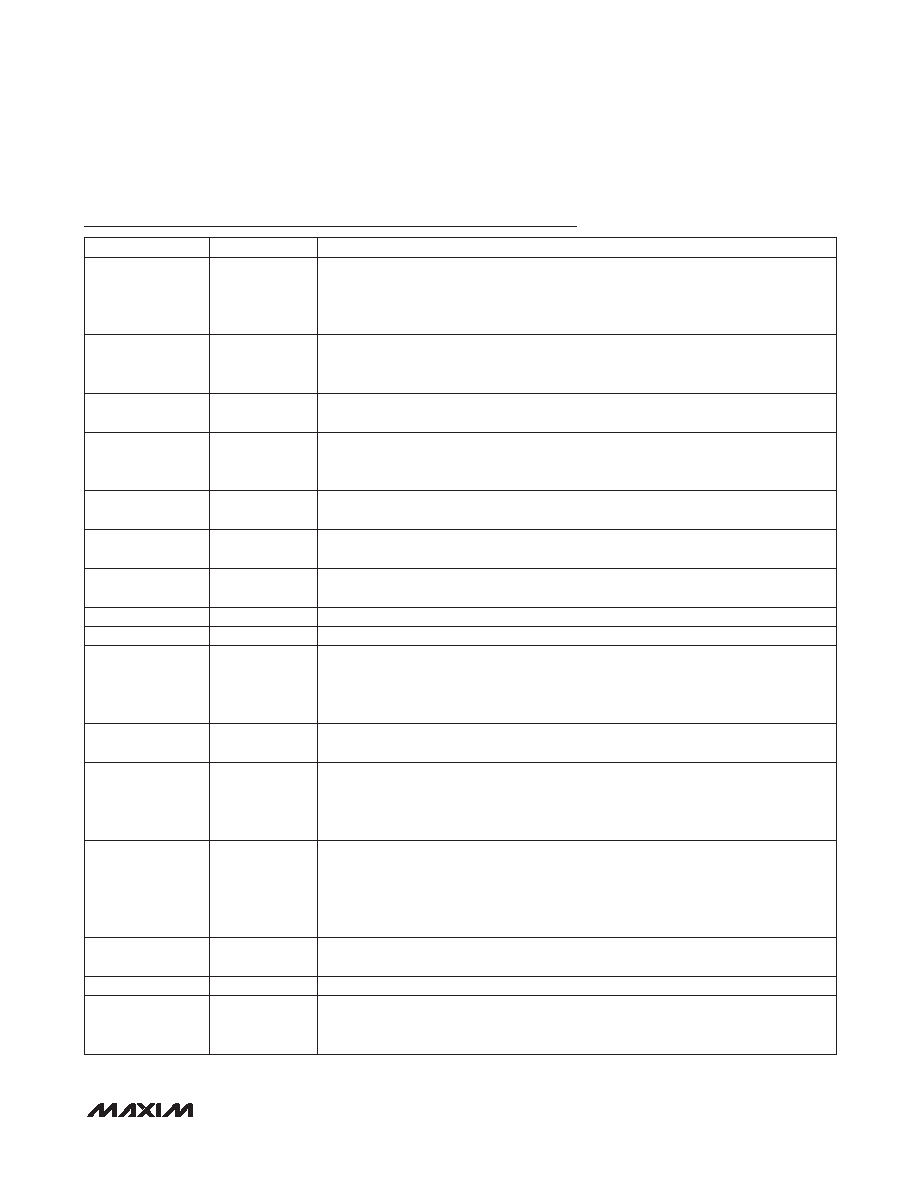

MAX9260 Pin Description

PIN

NAME

FUNCTION

1

ENABLE

Enable. Active-low parallel output-enable input requires external pulldown or pullup

resistors. Set ENABLE = low to enable PCLKOUT, SD, SCK, WS, and the parallel out-

puts, DOUT_. Set ENABLE = high to put PCLKOUT, SD, SCK, WS, and DOUT_ to high

impedance.

2

BWS

Bus-Width Select. Parallel output bus-width selection input requires external pulldown

or pullup resistors. Set BWS = low for 24-bit bus mode. Set BWS = high for 32-bit bus

mode.

3

INT

Interrupt. Interrupt input requires external pulldown or pullup resistors. A transition on

the INT input of the MAX9260 toggles the MAX9259’s INT output.

4

CDS

Control-Direction Selection. Control-link-direction selection input requires external pull-

down or pullup resistors. Set CDS = low for FC use on the MAX9259 side of the serial

link. Set CDS = high for FC use on the MAX9260 side of the serial link.

5

GPIO0

GPIO0. Open-drain general-purpose input/output with internal 60kI pullup resistors to

IOVDD. GPIO0 is high impedance during power-up and when PWDN = low.

6

ES

Edge Select. PCLKOUT edge-selection input requires external pulldown or pullup

resistors. Set ES = low for a rising-edge trigger. Set ES = high for a falling-edge trigger.

7, 63

AVDD

3.3V Analog Power Supply. Bypass AVDD to AGND with 0.1F and 0.001F capacitors

as close as possible to the device with the smallest value capacitor closest to AVDD.

8 , 9

IN+, IN-

Differential CML Input

+/-. Differential inputs of the serial link.

10, 64

AGND

Analog Ground

11

EQS

Equalizer Select. Deserializer equalizer-selection input requires external pulldown or

pullup resistors. The state of EQS latches upon power-up or rising edge of PWDN. Set

EQS = low for 10.7dB equalizer boost (EQTUNE = 1001). Set EQS = high for 5.2dB

equalizer boost (EQTUNE = 0100).

12

GPIO1

GPIO1. Open-drain general-purpose input/output with internal 60kI pullup resistors to

IOVDD. GPIO1 is high impedance during power-up and when PWDN = low.

13

DCS

Drive Current Select. Driver current-selection input requires external pulldown or pul-

lup resistors. Set DCS = high for stronger parallel data and clock output drivers. Set

DCS = low for normal parallel data and clock drivers (see the MAX9260 DC Electrical

Characteristics table).

14

MS

Mode Select. Control-link mode-selection/autostart mode selection input requires

external pulldown or pullup resistors. MS sets the control-link mode when CDS = high

(see the Control-Channel and Register Programming section). Set MS = low to select

base mode. Set MS = high to select the bypass mode. MS sets autostart mode when

CDS = low (see Tables 13 and 14).

15

DVDD

3.3V Digital Power Supply. Bypass DVDD to DGND with 0.1FF and 0.001FF capacitors

as close as possible to the device with the smaller value capacitor closest to DVDD.

16

DGND

Digital Ground

17

RX/SDA

Receive/Serial Data. UART receive or I2C serial-data input/output with internal 30kI

pullup to IOVDD. In UART mode, RX/SDA is the Rx input of the MAX9260’s UART. In

I2C mode, RX/SDA is the SDA input/output of the MAX9259’s I2C master.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX9271GTJ/V+ | IC SERIALIZER 16BIT GMSL 32TQFN |

| MAX9272GTM/V+ | IC DSERIALIZER 28BIT GMSL 48TQFN |

| MAX9273GTL/V+ | IC SERIALIZER 22BIT GMSL 40TQFN |

| MAX9390EHJ+ | IC CROSSPOINT SWITCH DUAL 32TQFP |

| MAX9392EHJ+ | IC CROSSPOINT SWITCH DUAL 32TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9263EVKIT+ | 制造商:Maxim Integrated Products 功能描述:GMSL SERIALIZER WITH HDCP - Boxed Product (Development Kits) |

| MAX9263GCB/V+ | 功能描述:串行器/解串器 - Serdes GMSL Serializer w/HDCP Interface RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9263GCB/V+T | 功能描述:串行器/解串器 - Serdes GMSL Serializer w/HDCP Interface RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9264EVKIT+ | 制造商:Maxim Integrated Products 功能描述:GMSL DESERIALIZER WITH HDCP - Boxed Product (Development Kits) |

| MAX9264GCB/V+ | 功能描述:串行器/解串器 - Serdes GMSL Deserializer w/HDCP Interface RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。