- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377879 > MB15F88UL (Fujitsu Limited) Fractional-N PLL Frequency Synthesizer PDF資料下載

參數(shù)資料

| 型號: | MB15F88UL |

| 廠商: | Fujitsu Limited |

| 英文描述: | Fractional-N PLL Frequency Synthesizer |

| 中文描述: | 分?jǐn)?shù)N PLL頻率合成器 |

| 文件頁數(shù): | 8/29頁 |

| 文件大?。?/td> | 175K |

| 代理商: | MB15F88UL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

MB15F88UL

8

I

FUNCTIONAL DESCRIPTION

1.

Serial Data Input

Serial data is entered using three pins, Data pin, Clock pin, and LE pin. Programmable dividers of TX/RX-PLL

sections and programmable reference dividers of TX/RX-PLL sections are controlled individually.

Serial data of binary code is entered through Data pin.

On a rising edge of clock, one bit of serial data is transferred into the shift register. On a rising edge of load

enable signal, the data stored in the shift register is transferred to one of latches depending upon the control bit

data setting.

Note : CN3

=

1 is prohibited

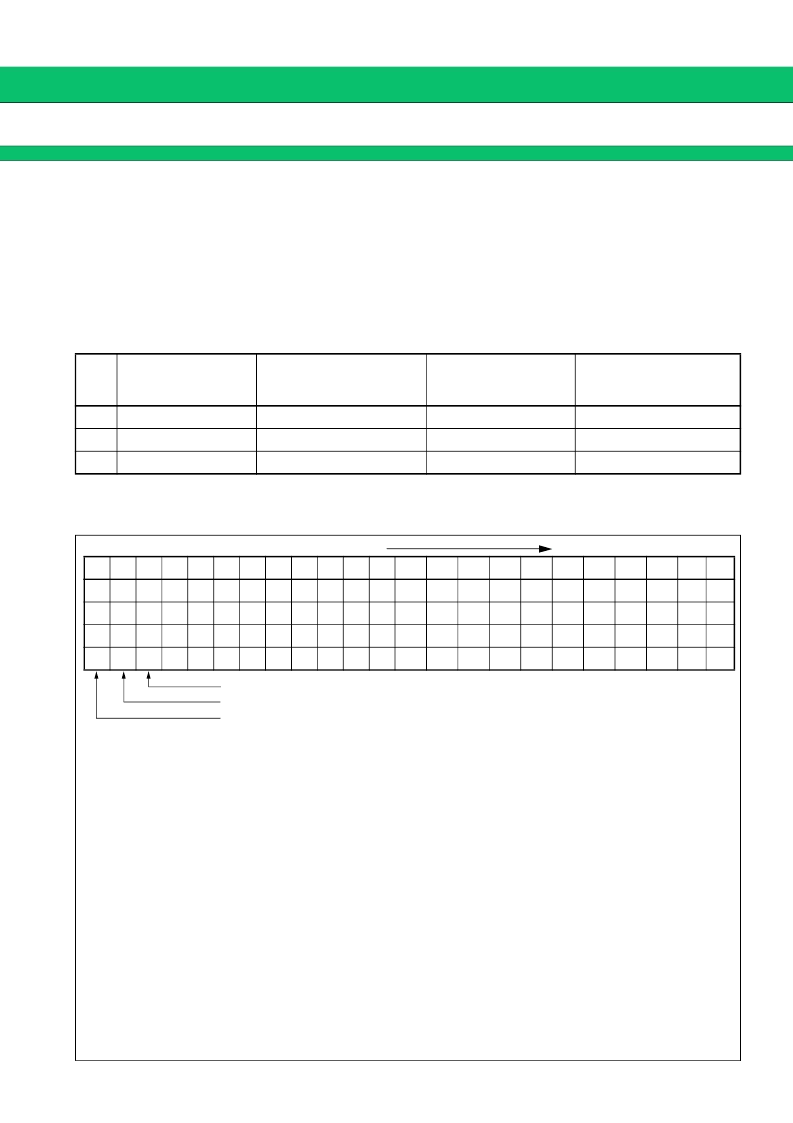

(1) Serial data format

The programmable

reference counter for

the TX-PLL

The programmable

counter and the swallow

counter for the TX-PLL

The programmable

reference counter for

the RX-PLL

The programmable

counter and the swallow

counter for the RX-PLL

CN1

0

1

0

1

CN2

0

0

1

1

CN3

0

0

0

0

Note: Data input with MSB first.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

0

0

0

R

C

1 R

C

2 R

C

3 R

C

4 R

C

5 R

C

6 R

C

7 R

C

8 R

C

9 R

C

10 R

C

11 R

C

12 R

C

13 R

C

14 LDS

T1

T2 SW

C

FC

C

CS

C

1

0

0

A

C

1 A

C

2 A

C

3 A

C

4 A

C

5

0

0

N

C

1 N

C

2 N

C

3 N

C

4 N

C

5 N

C

6 N

C

7 N

C

8 N

C

9 N

C

10 N

C

11 X

X

0

1

0

R

F

1 R

F

2 R

F

3 R

F

4 R

F

5 R

F

6 R

F

7 R

F

8 R

F

9 R

F

10 R

F

11 R

F

12 R

F

13 R

F

14 QM SC1 SC2

1

FC

F

CS

F

1

1

0

A

F

1 A

F

2 A

F

3 A

F

4 A

F

5 N

F

1 N

F

2 N

F

3 N

F

4 N

F

5 N

F

6 N

F

7 N

F

8 N

F

9 N

F

10 F1

F2

F3

F4

0

R

C

1 to R

C

14

A

C

1 to A

C

5

N

C

1 to N

C

11

LDS, T1, T2

SW

C

FC

C

CS

C

R

F

1 to R

F

14

A

F

1 to A

F

5

N

F

1 to N

F

10

F1 to F4

QM

SC1, SC2

FC

F

CS

F

X

: Divide ratio setting bits for the reference counter of the TX (8 to 16383)

: Divide ratio setting bits for the swallow counter of the TX (0 to 31, A

<

N)

: Divide ratio setting bits for the programmable counter of the TX (3 to 2047)

: Select bits for the lock detect output or a monitoring phase comparison frequency

: Divide ratio setting for the prescaler of the TX

: Phase control bit for the phase detector of the TX

: Charge pump current select bit of the TX

: Divide ratio setting bits for the reference counter of the RX (8 to 16383)

: Divide ratio setting bits for the swallow counter of the RX (0 to 31, A

<

N

2)

: Divide ratio setting bits for the programmable counter of the RX (34 to 1023)

: Fractional-N increment setting bit for the fractional accumulator (0 to 15, F

<

Q)

: Fractional-N modulus selection bit. “1” modulus

=

8, “0” modulus

=

5

: Spurious cancel set bit of the RX.

: Phase control bit for the phase detector of the RX.

: Charge pump current select bit of the RX

: Dummy bit (Set “0” or “1”)

LSB

MSB

Direction of data shift

Control bit (CN3)

Control bit (CN2)

Control bit (CN1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB15F88ULPFT | Fractional-N PLL Frequency Synthesizer |

| MB15F88ULPVA | Fractional-N PLL Frequency Synthesizer |

| MB15G000 | ASTRO-NT (for RF front-end LSI-Based on PLL, Analog Macro) |

| MB15S00 | IF Band Phase Locked Loop (PLL) Frequency Synthesizer(中頻鎖相環(huán)頻率合成器) |

| MB15S01 | IF Band Phase Locked Loop (PLL) Frequency Synthesizer(中頻鎖相環(huán)頻率合成器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB15F88ULPFT | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Fractional-N PLL Frequency Synthesizer |

| MB15F88ULPVA | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Fractional-N PLL Frequency Synthesizer |

| MB15F8XUL | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Fractional-N / Integer dual PLL Frequency Synthesizers |

| MB15G | 制造商:MICRO-ELECTRONICS 制造商全稱:Micro Electronics 功能描述:LED BACKLIGHT FOR LCD DISPLAY |

| MB15G000 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:ASTRO-NT (for RF front-end LSI-Based on PLL, Analog Macro) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。