- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376149 > MB90F823PFV (Electronic Theatre Controls, Inc.) 10-Bit Buffers/Drivers With 3-State Outputs 28-LCCC -55 to 125 PDF資料下載

參數(shù)資料

| 型號: | MB90F823PFV |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 10-Bit Buffers/Drivers With 3-State Outputs 28-LCCC -55 to 125 |

| 中文描述: | 16位微控制器專有 |

| 文件頁數(shù): | 44/98頁 |

| 文件大小: | 1415K |

| 代理商: | MB90F823PFV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

MB90820 Series

44

5.

16-bit reload timer (x 2)

The 16-bit reload timer provides two operating mode, internal clock mode and event count mode. In each

operating mode, the 16-bit down counter can be reloaded (reload mode) or stopped by underflow (one-shot

mode).

Output pins TO1 and TO0 are able to output different waveform according to the counter operating mode. TO1

and TO0 toggles when counter underflows if counter is operated as reload mode. TO1 and TO0 output specified

level (H or L) during counting if the counter is in one-shot mode.

Features of the 16-bit reload timer :

Interrupt when timer underflows

Supports for EI

2

OS

Internal clock operating mode :

Three internal count clocks can be selected.

Counter can be activated by software or external trigger (signal at TIN1 and TIN0 pins).

Counter can be reloaded or stopped when underflow after activated.

Event count operating mode :

Counter counts down one by one with specified edge at TIN1 and TIN0 pins.

Counter can be reloaded or stopped when underflow.

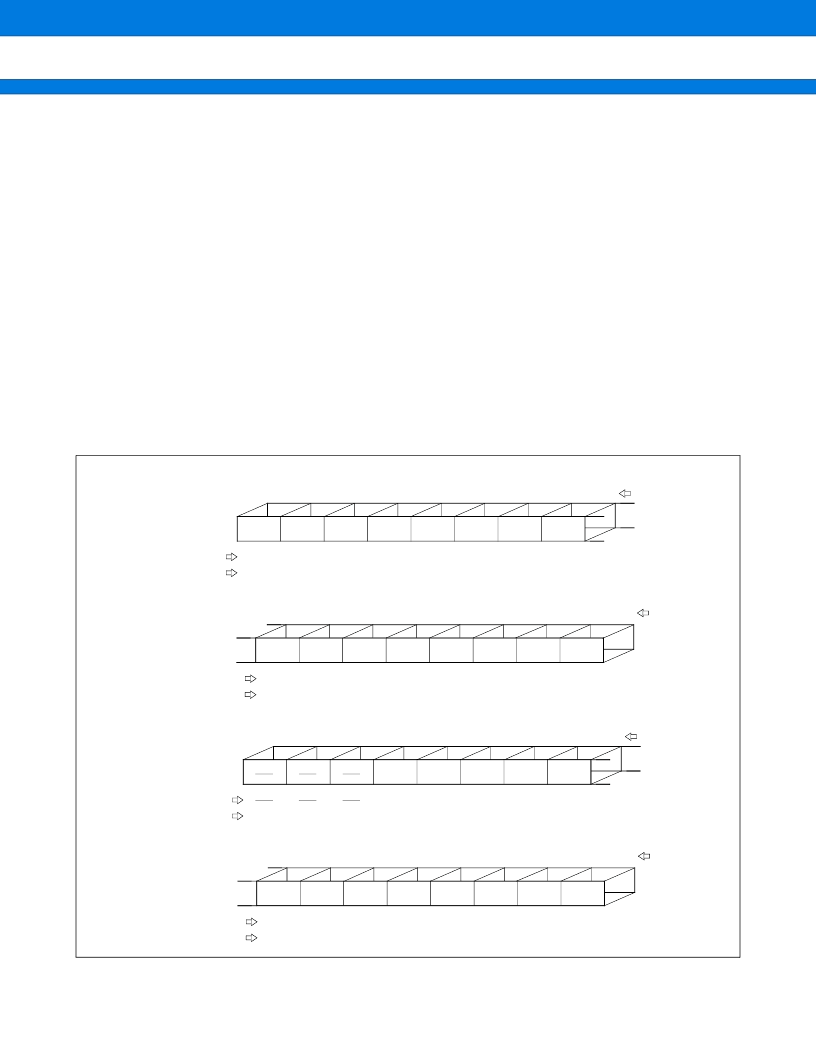

(1) Register configuration

Note : Registers TMR0, TMR1/TMRD0, TMRD1 are word access only.

15

14

13

12

11

10

9

8

Bit

16-bit Timer Register/16-bit Reload Timer Register (Upper)

7

6

5

4

3

2

1

0

Bit

16-bit Timer Register/16-bit Reload Timer Register (Lower)

Address: ch0 000085

H

ch1 000089

H

TMR0

,

TMR1 /

TMRD0

,

TMRD1

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

Initial value

Read/write

Address: ch0 000084

H

ch1 000088

H

Initial value

Read/write

TMR0

,

TMR1 /

TMRD0

,

TMRD1

D15

D14

D13

D12

D11

D10

D09

D08

D07

D06

D05

D04

D03

D02

D01

D00

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

R/W

X

15

14

13

12

11

10

9

8

Bit

Timer Control Status Register (Upper)

7

6

5

4

3

2

1

0

Bit

Timer Control Status Register (Lower)

Address: ch0 000083

H

ch1 000087

H

TMCSRH0

,

TMCSRH1

R/W

0

R/W

0

R/W

0

R/W

0

Initial value

Read/write

Address: ch0 000082

H

ch1 000086

H

Initial value

Read/write

TMCSRL0

,

TMCSRL1

CSL1

CSL0

MOD2 MOD1

MOD0 OUTE

OUTL RELD

INTE

UF

CNTE

TRG

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

FSEL

R/W

1

X

X

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB90822PFV | 10-Bit Buffers/Drivers With 3-State Outputs 24-CFP -55 to 125 |

| MB90822 | 16-bit Proprietary Microcontroller |

| MB90822PF | 16-bit Proprietary Microcontroller |

| MB90822PFM | 16-bit Proprietary Microcontroller |

| MBI5169 | 8 bit CONSTANT CURRENT LED SINK DRIVER WITH ERROR DETECTION |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB90F867APFR-G-SNE1 | 制造商:FUJITSU 功能描述: |

| MB90F867ASPF-GE1 | 制造商:FUJITSU 功能描述:IC 16BIT MCU I2C SMD QFP100 |

| MB90F867ASPFR-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F867ASPFR-G-SPE1 | 制造商:FUJITSU 功能描述: |

| MB90F897PMCR-G-TE1 | 制造商:FUJITSU 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。