- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377930 > MB90M408 (Fujitsu Limited) Octal Edge-Triggered D-type Flip-Flops With Clear 20-CDIP -55 to 125 PDF資料下載

參數(shù)資料

| 型號: | MB90M408 |

| 廠商: | Fujitsu Limited |

| 英文描述: | Octal Edge-Triggered D-type Flip-Flops With Clear 20-CDIP -55 to 125 |

| 中文描述: | F2MC - 16LX系列16位微控制器硬件手冊英文摘要 |

| 文件頁數(shù): | 9/28頁 |

| 文件大小: | 213K |

| 代理商: | MB90M408 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

GENERAL

1-5

1.3

Product Lineup

Table 1-1

lists the Monolith (MB90M405) series product lineup. Functions other than the ROM/RAM capacity

are shared.

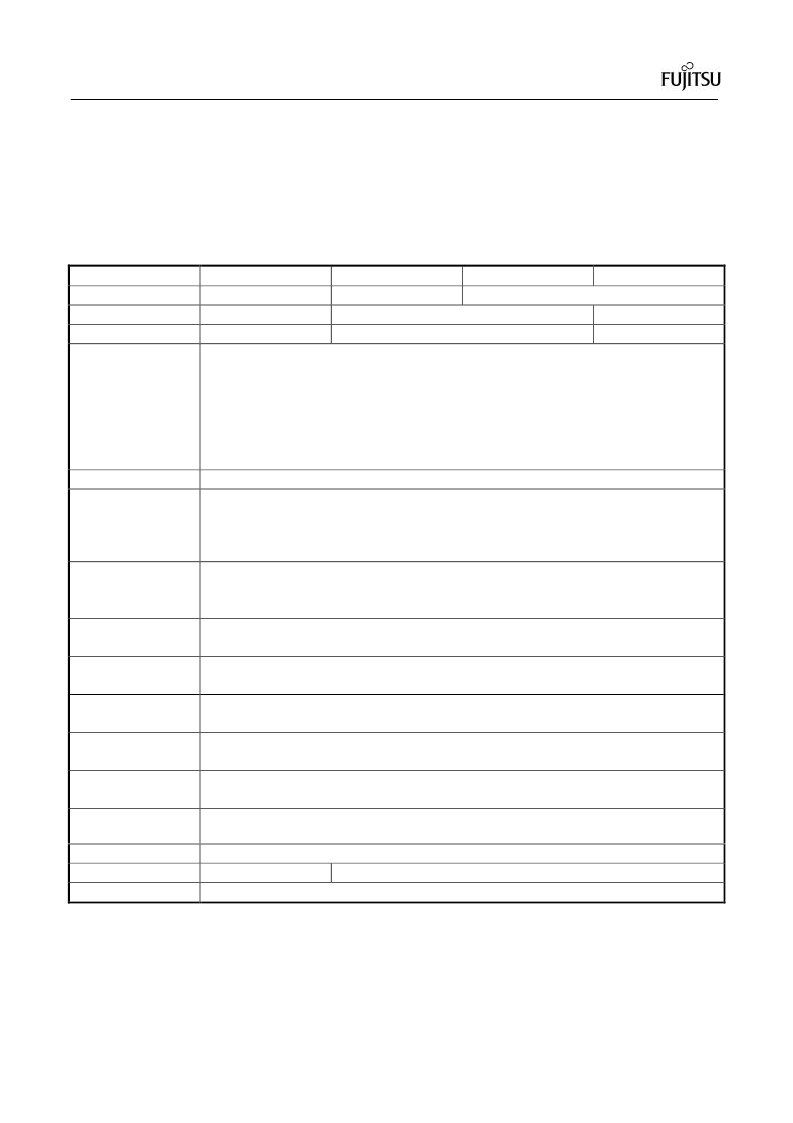

Table 1-1 MB90M405 Series Product Lineup

Product name

Classification

ROM capacity

RAM capacity

MB90MV405

Evaluate

Not provided

4 Kbytes

Count of basic instructions: 351

Minimum instruction execution time:

MB90MF408

Flash Type ROM

MB90M408

Mass-produced product (mask ROM)

128 Kbytes

4 Kbytes

MB90M407

96 Kbytes

4 Kbytes

CPU Function

59.5 ns (at original oscillation of 4.2 MHz, with

PLL clock generated by multiplying original

oscillation by 4)

Addressing types: 23

Program patch function: 2-address pointer

Maximum memory space: 16 Mbytes

I/O port (CMOS) 26 pins (all of 26 pins also serve as resource pins)

60 FL output pins can be used (Under LED control, 43 FL output pins and 17 LED

control pins are required).

Enables FL driver control and LED driver control can be performed.

Under FL driver control, the dimmer can be set for both digits and segments.

Can also be used as the clock-synchronous method extended I/O serial.

A dedicated baud rate generator is built-in.

Four channels are built-in (two channels also serve as UART channels).

16-bit reload timer operation (Toggle output or one-shot output can be selected.)

An event count function can be selected. Three channels are built-in.

16-bit output compare x 1 channel (for clearing free-run timer)

16-bit input capture x 2 channels

8-/10-bit resolution x 16 channels (input multiplex)

Minimum conversion time: 6.2 μs (at internal operation of 16 MHz)

The external input clock can be divided and output to the outside.

Clock division rates: 16, 32, 64, or 128 (programmable)

Four independent channels (also serve for A/D input)

Interrupt factor: L

→

H edge, H

→

L edge, L level, or H level

Sleep mode, stop mode, CPU intermittent mode, or pseudo-timer mode

Port

FL Controller

Serial I/O (UART)

16-bit reload timer

16-bit free-run timer

8-/10-bit A/D

converter

Timer clock divider

External interrupt

Low power

consumption mode

Process

Package

Operating voltage

CMOS

QFP-100 (0.65 mm pitch)

PGA256

3.3 V

±

0.3 V(16.8 MHz: 4.2 MHz multiplied by 4)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB90MV405 | F2MC-16LX FAMILY 16-BIT MICROCONTROLLERS HARDWARE MANUAL ABSTRACTS |

| MB90M407APF | 16-Bit Original Microcontroller |

| MB90M407PF | 16-Bit Original Microcontroller |

| MB90M408APF | 16-Bit Original Microcontroller |

| MB90M408PF | 16-Bit Original Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB90V340A-102CR | 制造商:FUJITSU 功能描述: |

| MB-910 | 制造商:Circuit Test 功能描述:BREADBOARD WIRING KIT - 350 PCS |

| MB9100100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB9100-100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB91101 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。