- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371008 > MC13109AFB (MOTOROLA INC) UNIVERSAL CORDLESS TELEPHONE SUBSYSTEM IC PDF資料下載

參數(shù)資料

| 型號(hào): | MC13109AFB |

| 廠商: | MOTOROLA INC |

| 元件分類(lèi): | 無(wú)繩電話(huà)/電話(huà) |

| 英文描述: | UNIVERSAL CORDLESS TELEPHONE SUBSYSTEM IC |

| 中文描述: | TELECOM, CORDLESS, RF AND BASEBAND CIRCUIT, PQFP52 |

| 封裝: | PLASTIC, QFP-52 |

| 文件頁(yè)數(shù): | 15/28頁(yè) |

| 文件大小: | 1307K |

| 代理商: | MC13109AFB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

MC13109A

15

MOTOROLA RF/IF DEVICE DATA

ELECTRICAL CHARACTERISTICS (continued)

(VCC = 2.6 V, TA = 25

°

C)

Characteristic

Unit

Max

Typ

Min

Symbol

Measure

Pin

Condition

PLL PIN INTERFACE

EN to Clk Setup Time

–

EN, Clk

tsuEC

tsuDC

th

trec

tw

tr, tf

200

–

–

ns

Data to Clk Setup Time

–

Data, Clk

100

–

–

ns

Hold Time

–

Data, Clk

90

–

–

ns

Recovery Time

–

EN, Clk

90

–

–

ns

Input Pulse Width

–

EN, Clk

100

–

–

ns

Input Rise and Fall Time

–

Data

Clk

EN

–

–

9.0

μ

s

MPU Interface

Power–Up Delay

90% of PLL Vref to

Data, Clk, EN

–

tpuMPU

–

100

–

μ

s

PLL LOOP

2nd LO Frequency

–

LO2 In

LO2 Out

fLO

–

–

12

MHz

“Tx VCO” Input Frequency

Vin = 200 mVpp

Tx VCO

ftxmax

–

–

80

MHz

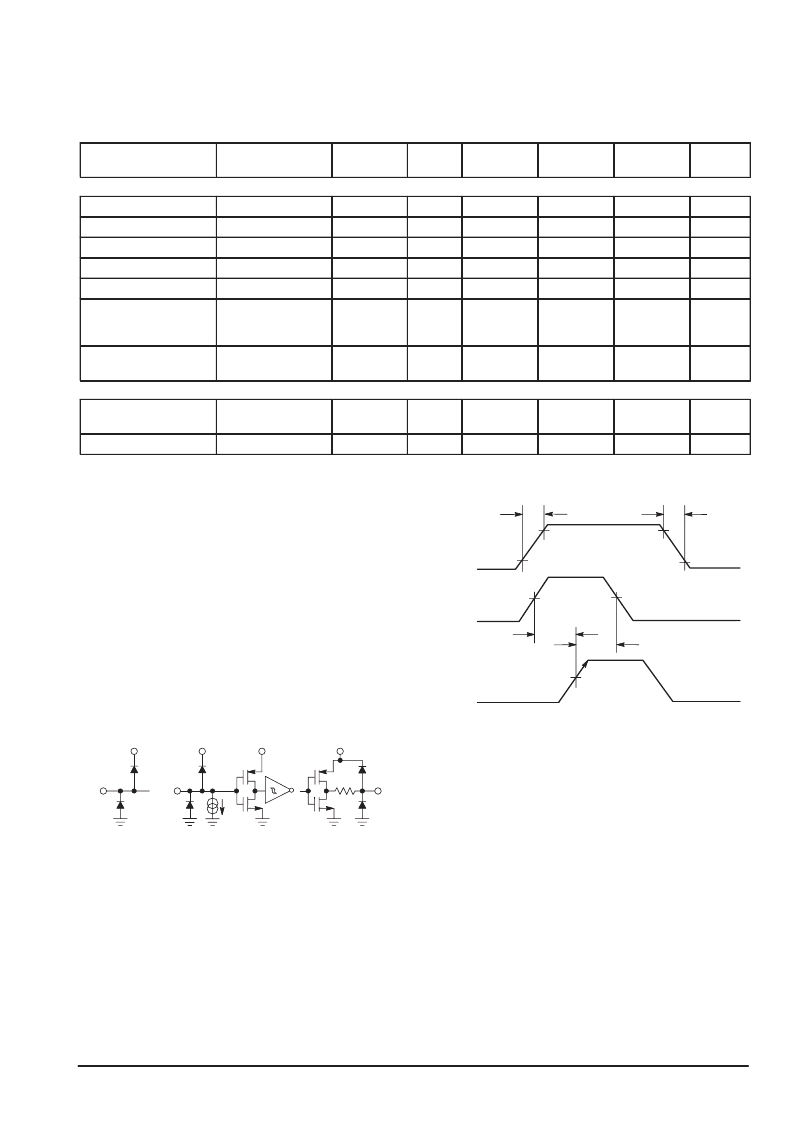

PLL I/O Pin Specifications

The 2nd LO, Rx and Tx PLL’s and MPU serial interface are

normally powered by the internal voltage regulator at the “PLL

Vref” pin. The “PLL Vref” pin is the output of a voltage regulator

which is powered from the “V

CC

Audio” power supply pin.

Therefore, the maximum input and output levels for most PLL

I/O pins (LO2 In, LO2 Out, Rx PD, Tx PD, Tx VCO) is the

regulated voltage at the “PLL Vref” pin. The ESD protection

diodes on these pins are also connected to “PLL Vref”.

Internal level shift buffers are provided for the pins (Data, Clk,

EN, Clk Out) which connect directly to the microprocessor.

The maximum input and output levels for these pins is V

CC

.

Figure 5 shows a simplified schematic of the PLL I/O pins.

Figure 5. PLL I/O Pin Simplified Schematics

PLL Vref

(2.2 V)

In

I/O

VCC Audio

(2.0 to 5.5 V)

PLL Vref

(2.2 V)

VCC Audio

(2.0 to 5.5 V)

Clk Out Pin

Data, Clk, and EN Pins

LO2 In, LO2 Out,

Rx PD, Tx PD and

Tx VCO Pins

Out

2.0

μ

A

1.0 k

Microprocessor Serial Interface

The “Data”, “Clk”, and “EN” pins provide an MPU serial

interface for programming the reference counters, the

transmit and receive channel divider counter and various

control functions. The “Data” and “Clk” pins are used to load

data into the shift register. Figure 6 shows “Data” and “Clk”

pin timing. Data is clocked on positive clock transitions.

Figure 6. Data and Clock Timing Requirement

Data,

Clk, EN

Data

Clk

tsuDC

tr

tf

50%

50%

th

10%

90%

After data is loaded into the shift register, the data is

latched into the appropriate latch register using the “EN” pin.

This is done in two steps. First, an 8–Bit address is loaded

into the shift register and latched into the 8–Bit address latch

register. Then, up to 16–Bits of data is loaded into the shift

register and latched into the data latch register specified by

the address that was previously loaded. Figure 7 shows the

timing required on the EN pin. Latching occurs on the

negative EN transition.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC13109AFTA | UNIVERSAL CORDLESS TELEPHONE SUBSYSTEM IC |

| MC13110A | Narrowband FM IF Receiver(窄頻帶FM IF 接收器) |

| MC13111A | Narrowband FM IF Receiver(窄頻帶FM IF 接收器) |

| MC13111BFTA | UNIVERSAL NARROWBAND FM RECEIVER INTEGRATED CIRCUIT |

| MC13110 | UNIVERSAL NARROWBAND FM RECEIVER INTEGRATED CIRCUIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC13109AFTA | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:UNIVERSAL CORDLESS TELEPHONE SUBSYSTEM IC |

| MC13109FB | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:Universal Cordless Telephone Subsystem IC |

| MC13109FTA | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:Universal Cordless Telephone Subsystem IC |

| MC1310DIN | 功能描述:電源線(xiàn)濾波器 Filter 500V 10A RoHS:否 制造商:EPCOS 電壓額定值:277 VAC 電流額定值:100 A 安裝風(fēng)格:Chassis 端接類(lèi)型:Screw |

| MC1310DIN-HFP | 制造商:TDK-Lambda Corporation 功能描述:FILTER500VAC, 3 PHASE10A,, HAZMAT - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。