- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371009 > MC14046BCL (MOTOROLA INC) Phase Locked Loop PDF資料下載

參數(shù)資料

| 型號(hào): | MC14046BCL |

| 廠商: | MOTOROLA INC |

| 元件分類: | XO, clock |

| 英文描述: | Phase Locked Loop |

| 中文描述: | PHASE LOCKED LOOP, 1 MHz, CDIP16 |

| 封裝: | CERAMIC, DIP-16 |

| 文件頁(yè)數(shù): | 5/7頁(yè) |

| 文件大小: | 253K |

| 代理商: | MC14046BCL |

MOTOROLA CMOS LOGIC DATA

5

MC14046B

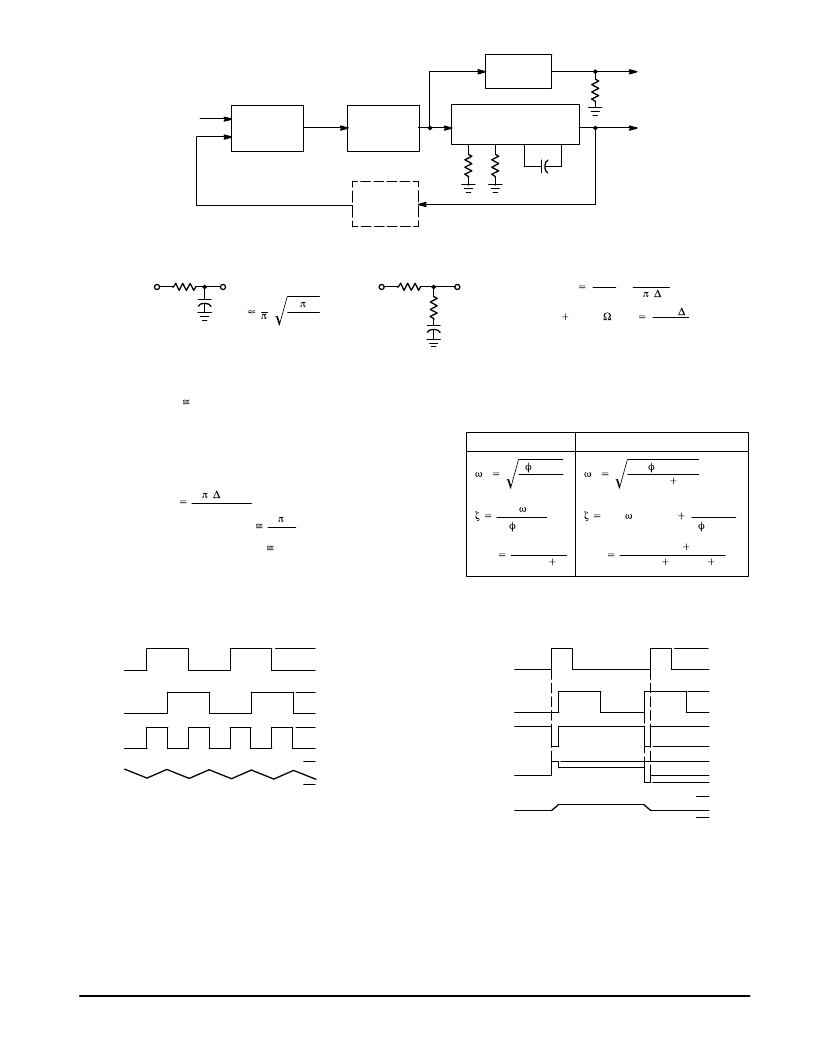

Typical Low–Pass Filters

NOTE: Sometimes R3 is split into two series resistors each R3

÷

2. A capacitor CC is then placed from the midpoint to ground. The value for

CC should be such that the corner frequency of this network does not significantly affect

ω

n. In Figure B, the ratio of R3 to R4 sets the

damping, R4

(0.1)(R3) for optimum results.

Figure 3. General Phase–Locked Loop Connections and Waveforms

Waveforms

Note: for further information, see:

(1) F. Gardner, “Phase–Lock Techniques”, John Wiley and Son, New York, 1966.

(2) G. S. Moschytz, “Miniature RC Filters Using Phase–Locked Loop”, BSTJ, May, 1965.

(3) Garth Nash, “Phase–Lock Loop Design Fundamentals”, AN–535, Motorola Inc.

(4) A. B. Przedpelski, “Phase–Locked Loop Design Articles”, AR254, reprinted by Motorola Inc.

PCAin

@ FREQUENCY f

′

PCBin

14

3

PHASE

COMPARATOR

EXTERNAL

LOW–PASS

FILTER

VCO

2 OR 13

PC1out

OR

PC2out

VCOin

9

9

10

4

EXTERNAL

÷

N

COUNTER

R1

R2

11

12

6

7

CIA

CIB

CI

SFout

RSF

VCOout

@ FREQUENCY Nf

′

= f

(a)

INPUT

R3

OUTPUT

C2

2fC

1

2

R3 C2

fL

(a)

INPUT

R3

OUTPUT

R4

C2

Typically:

R4C2

6N

fmax

–

N

2

f

(R3

3,000 ) C2

100N f

fmax2

– R4C2

f = fmax – fmin

Definitions:

N = Total division ratio in feedback loop

K

φ

= VDD/

π

for Phase Comparator 1

K

φ

= VDD/4

π

for Phase Comparator 2

2

fVCO

VDD– 2 V

for a typical design

ω

n

KVCO

2

fr

10

0.707

(at phase detector input)

ζ

LOW–PASS FILTER

Filter A

Filter B

n

K KVCO

NR3C2

N n

2K KVCO

F(s)

1

R3C2S

1

n

K KVCO

NC2(R3

R4)

0.5

n(R3C2

K N

F(s)

R3C2S

1

S(R3C2

R4C2)

1

PCAin

PCBin

PC1out

VCOin

VDD

VSS

VOH

VOL

VOH

VOL

VOH

VOL

PCAin

PCBin

PC2out

VCOin

LD

VDD

VSS

VOH

VOL

VOH

VOL

VOH

VOL

VOL

VOH

Phase Comparator 1

Phase Comparator 2

SOURCE

FOLLOWER

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC14046 | Phase Locked Loop |

| MC14046BDW | Phase Locked Loop |

| MC1405 | ANALOG - TO - DIGITAL CONVERTER SUBSYSTEM |

| MC14070 | CMOS SSI Quad Exclusive OR and NOR Gates |

| MC14077BCP | IEEE 802.3af PoE Powered Device Controllers 8-TSSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14046BCP | 功能描述:鎖相環(huán) - PLL LOG CMOS PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| MC14046BCPG | 功能描述:鎖相環(huán) - PLL 3-18V RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| MC14046BDW | 功能描述:鎖相環(huán) - PLL LOG CMOS PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| MC14046BDWG | 功能描述:鎖相環(huán) - PLL LOG CMOS PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| MC14046BDWR2 | 功能描述:鎖相環(huán) - PLL LOG CMOS PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。