- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45211 > MC68332GVPV25 (MOTOROLA INC) 32-BIT, 25 MHz, MICROCONTROLLER, PQFP144 PDF資料下載

參數(shù)資料

| 型號: | MC68332GVPV25 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 25 MHz, MICROCONTROLLER, PQFP144 |

| 封裝: | PLASTIC, LQFP-144 |

| 文件頁數(shù): | 75/111頁 |

| 文件大小: | 650K |

| 代理商: | MC68332GVPV25 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁當前第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁

MOTOROLA

MC68332

66

MC68332TS/D

6.3 Pin Function

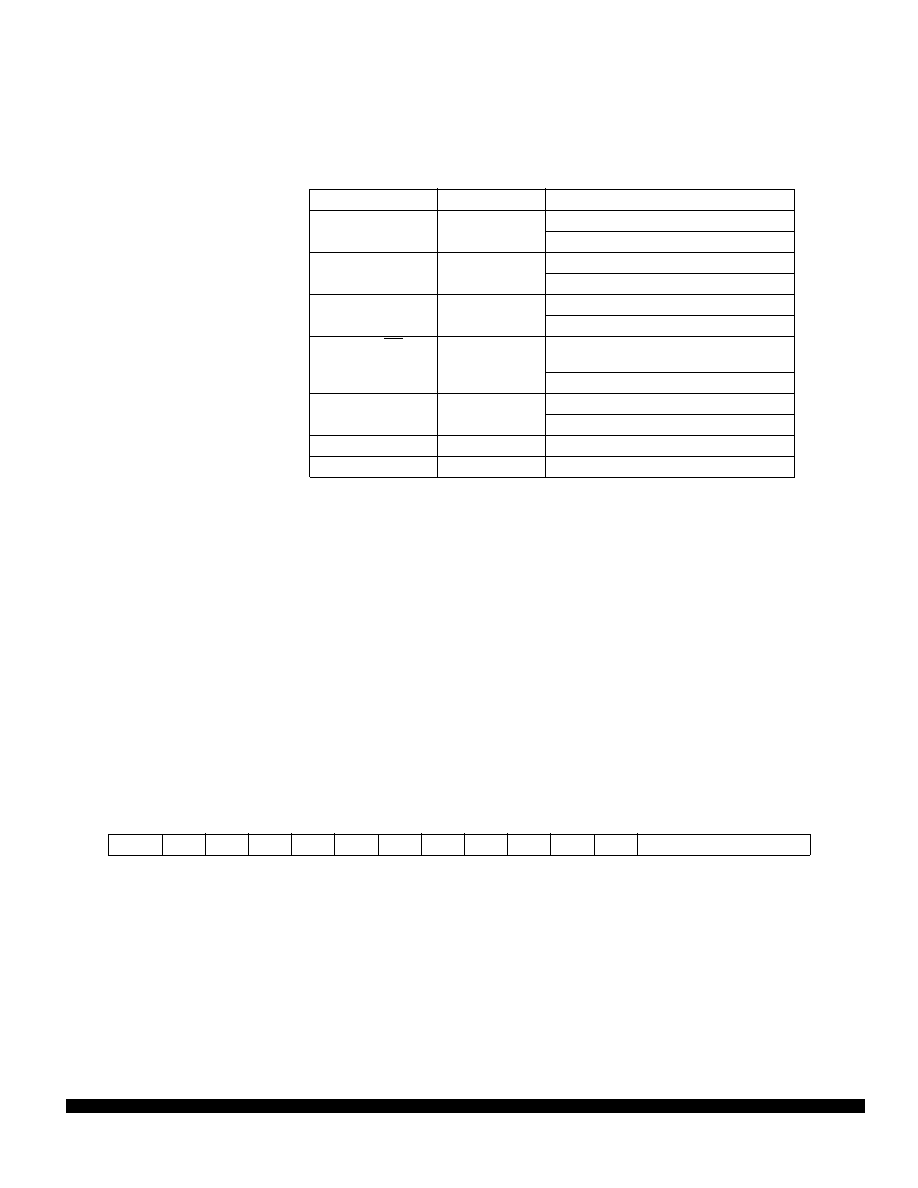

The following table is a summary of the functions of the QSM pins when they are not configured for gen-

eral-purpose I/O. The QSM data direction register (DDRQS) designates each pin except RXD as an in-

put or output.

6.4 QSM Registers

QSM registers are divided into four categories: QSM global registers, QSM pin control registers, QSPI

submodule registers, and SCI submodule registers. The QSPI and SCI registers are defined in separate

sections below. Writes to unimplemented register bits have no meaning or effect, and reads from unim-

plemented bits always return a logic zero value.

The module mapping bit of the SIM configuration register (SIMCR) defines the most significant bit

(ADDR23) of the address, shown in each register figure as Y (Y = $7 or $F). This bit, concatenated with

the rest of the address given, forms the absolute address of each register. Refer to the SIM section of

this technical summary for more information about how the state of MM affects the system.

6.4.1 Global Registers

The QSM global registers contain system parameters used by both the QSPI and the SCI submodules.

These registers contain the bits and fields used to configure the QSM.

The QSMCR contains parameters for the QSM/CPU/intermodule bus (IMB) interface.

STOP — Stop Enable

0 = Normal QSM clock operation

1 = QSM clock operation stopped

STOP places the QSM in a low-power state by disabling the system clock in most parts of the module.

The QSMCR is the only register guaranteed to be readable while STOP is asserted. The QSPI RAM is

not readable. However, writes to RAM or any register are guaranteed to be valid while STOP is assert-

ed. STOP can be negated by the CPU and by reset.

Pin

Mode

Pin Function

MISO

Master

Serial Data Input to QSPI

QSPI Pins

Slave

Serial Data Output from QSPI

MOSI

Master

Serial Data Output from QSPI

Slave

Serial Data Input to QSPI

SCK

Master

Clock Output from QSPI

Slave

Clock Input to QSPI

PCS0/SS

Master

Input: Assertion Causes Mode Fault

Output: Selects Peripherals

Slave

Input: Selects the QSPI

PCS[3:1]

Master

Output: Selects Peripherals

Slave

None

SCI Pins

TXD

Transmit

Serial Data Output from SCI

RXD

Receive

Serial Data Input to SCI

QSMCR — QSM Configuration Register

$YFFC00

15

14

13

12

11

10

9

8

7

6

5

4

3

0

STOP

FRZ1

FRZ0

0

SUPV

0

IARB

RESET:

0

1

0

相關PDF資料 |

PDF描述 |

|---|---|

| MC68332GVFC25 | 32-BIT, 25 MHz, MICROCONTROLLER, PQFP132 |

| MC68332GCPV20 | 32-BIT, 20.97 MHz, MICROCONTROLLER, PQFP144 |

| MC68LK332ACPV16 | 32-BIT, 16.78 MHz, MICROCONTROLLER, PQFP144 |

| MCW68332A | 32-BIT, MICROCONTROLLER, UUC |

| MC68332GVFC16 | 32-BIT, 16 MHz, MICROCONTROLLER, PQFP132 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC68332MFC16 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68332MFC20 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68332MFV16 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68332MFV20 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68332TS | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。