- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371046 > MC68C912B32FU8 (MOTOROLA INC) 16-Bit Microcontroller PDF資料下載

參數(shù)資料

| 型號: | MC68C912B32FU8 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-Bit Microcontroller |

| 中文描述: | 16-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | QFP-80 |

| 文件頁數(shù): | 99/128頁 |

| 文件大?。?/td> | 748K |

| 代理商: | MC68C912B32FU8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁當(dāng)前第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

MC68HC912B32

MC68HC912B32TS/D

MOTOROLA

99

14.3 Loopback Modes

Two loopback modes are used to determine the source of bus faults.

Digital Loopback

is used to determine if a bus fault has been caused by failure in the node’s internal

circuits or elsewhere in the network, including the node’s analog physical interface. In this mode, the

receive digital input (RxPD) is disconnected from the analog transceiver’s receive output. RxPD is then

connected internally to the transmit digital output (TxPD) to form the loopback connection. The analog

transceiver’s transmit input is still driven by TxPD in this mode.

Analog Loopback

is used to determine if a bus fault has been caused by a failure in the node's off-chip

analog transceiver or elsewhere in the network. The BDLC analog loopback mode does not modify the

digital transmit or receive functions of the BDLC. It does, however, ensure that once analog loopback

mode is exited, the BDLC will wait for an idle bus condition before participation in network communica-

tion resumes. If the off-chip analog transceiver has a loopback mode, it usually causes the input to the

output drive stage to be looped back into the receiver, allowing the node to receive messages it has

transmitted without driving the J1850 bus. In this mode, the output to the J1850 bus is typically high

impedance. This allows the communication path through the analog transceiver to be tested without in-

terfering with network activity. Using the BDLC analog loopback mode in conjunction with the analog

transceiver's loopback mode ensures that, once the off-chip analog transceiver has exited loopback

mode, the BDLC will not begin communicating before a known condition exists on the J1850 bus.

14.4 BDLC Registers

Eight registers are available for controlling operation of the BDLC and for communicating data and sta-

tus information. A full description of each register follows.

IMSG — Ignore Message

Disables the receiver until a new start-of-frame (SOF) is detected.

0 = Enable Receiver

1 = Disable Receiver

CLKS — Clock Select

Designates nominal BDLC operating frequency (f

bdlc

) for J1850 bus communication and automatic ad-

justment of symbol time.

0 = Integer frequency (1 MHz)

1 = Binary frequency (1.048576 MHz)

R1, R0 — Rate Select

Determines the divisor of the MCU system clock frequency (f

TCLKS

) to form the BLDC operating fre-

quency (f

BDLC

). These bits may be written only once after reset.

The selected value depends upon the MCU system clock frequency according to

Table 32

or

Table 33

.

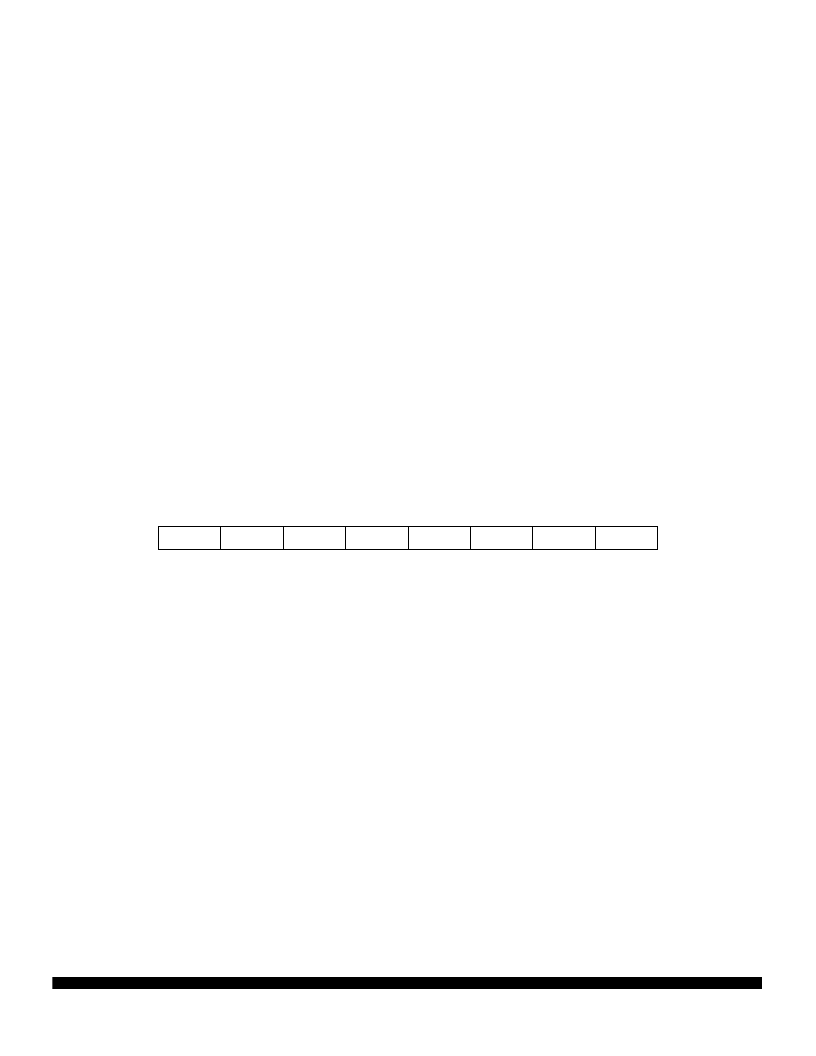

BCR1 —

BDLC Control Register 1

$00F8

Bit 7

6

5

4

3

2

1

Bit 0

IMSG

CLCKS

R1

R0

0

0

IE

WCM

RESET:

1

1

1

0

0

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68B912B32FU8 | 16-Bit Microcontroller |

| MC68C912B32CFU8 | 16-Bit Microcontroller |

| MC68CK338 | Highly Integrated, Low-Power, 32-Bit Microcontroller |

| MC68EC060 | 32-Bit Microprocessors.(32位微處理器) |

| MC68EN360RC25V | QUad Integrated Communications Controller Users Manual |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68CK16Z1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

| MC68CK16Z1CAG16 | 功能描述:16位微控制器 - MCU 16BIT 1KRAM 32KHZ CRYSTAL RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時鐘頻率:24 MHz 程序存儲器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MC68CK16Z1CAG16 | 制造商:Freescale Semiconductor 功能描述:Microcontroller |

| MC68CK16Z1CFC16 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

| MC68CK16Z1CPV16 | 功能描述:16位微控制器 - MCU 16 Bit 16MHz RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時鐘頻率:24 MHz 程序存儲器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。