- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359147 > MC7445ARX1000LF (飛思卡爾半導(dǎo)體(中國(guó))有限公司) RISC Microprocessor Hardware Specifications PDF資料下載

參數(shù)資料

| 型號(hào): | MC7445ARX1000LF |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | RISC Microprocessor Hardware Specifications |

| 中文描述: | RISC微處理器硬件規(guī)格 |

| 文件頁(yè)數(shù): | 37/64頁(yè) |

| 文件大小: | 1127K |

| 代理商: | MC7445ARX1000LF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

MPC7455 RISC Microprocessor Hardware Specifications, Rev. 4.1

Freescale Semiconductor

37

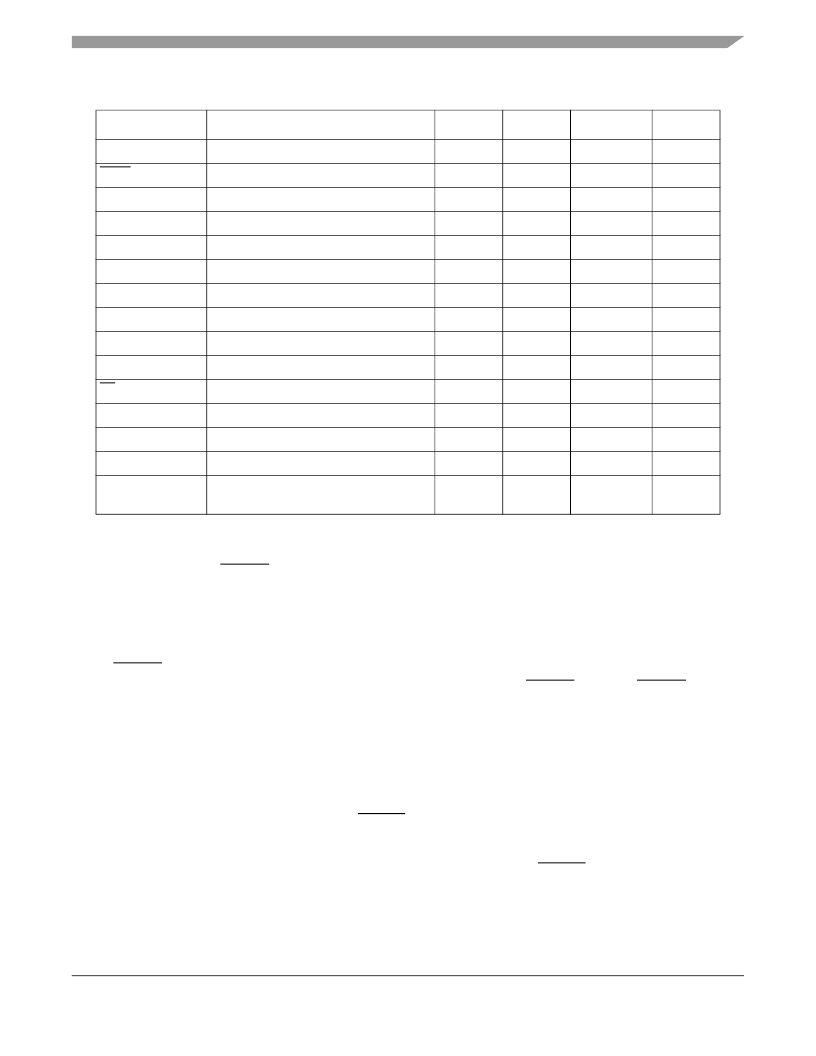

Pinout Listings

TBEN

E1

High

Input

BVSEL

TBST

F11

Low

Output

BVSEL

TCK

C6

High

Input

BVSEL

TDI

B9

High

Input

BVSEL

7

TDO

A4

High

Output

BVSEL

TEA

L1

Low

Input

BVSEL

TEST[0:3]

A12, B6, B10, E10

—

Input

BVSEL

2

TEST[4]

D10

—

Input

BVSEL

9

TMS

F1

High

Input

BVSEL

7

TRST

A5

Low

Input

BVSEL

7, 14

TS

L4

Low

I/O

BVSEL

8

TSIZ[0:2]

G6, F7, E7

High

Output

BVSEL

TT[0:4]

E5, E6, F6, E9, C5

High

I/O

BVSEL

WT

D3

Low

Output

BVSEL

8

V

DD

H8, H10, H12, J7, J9, J11, J13, K8, K10,

K12, K14, L7, L9, L11, L13, M8, M10, M12

—

—

N/A

Notes:

1. OV

DD

supplies power to the processor bus, JTAG, and all control signals; and V

DD

supplies power to the processor

core and the PLL (after filtering to become AV

DD

). To program the I/O voltage, connect BVSEL to either GND

(selects 1.8 V) or to HRESET (selects 2.5 V). If used, the pulldown resistor should be less than 250

. For actual

recommended value of V

in

or supply voltages see

Table 4

.

2. These input signals are for factory use only and must be pulled up to OV

DD

for normal machine operation.

3. These signals are for factory use only and must be left unconnected for normal machine operation.

4. Ignored in 60x bus mode.

5. This signal selects between MPX bus mode (asserted) and 60x bus mode (negated) and will be sampled at

HRESET going high.

6. This signal must be negated during reset, by pull-up to OV

DD

or negation by HRESET (inverse of HRESET), to

ensure proper operation.

7. Internal pull-up on die.

8. These pins require weak pull-up resistors (for example, 4.7 k

) to maintain the control signals in the negated state

after they have been actively negated and released by the MPC7445 and other bus masters.

9. These input signals are for factory use only and must be pulled down to GND for normal machine operation.

10.This pin can externally cause a performance monitor event. Counting of the event is enabled via software.

11.Unused address pins must be pulled down to GND.

12.This test signal is recommended to be tied to HRESET; however, other configurations will not adversely affect

performance.

13.These signals must be pulled down to GND if unused, or if the MPC7445 is in 60x bus mode.

14.This signal must be asserted during reset, by pull-down to GND or assertion by HRESET, to ensure proper

operation.

Table 15. Pinout Listing for the MPC7445, 360 CBGA Package (continued)

Signal Name

Pin Number

Active

I/O

I/F Select

1

Notes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC7445ARX1000LG | RISC Microprocessor Hardware Specifications |

| MC7447A | PowerPC microprocessor |

| MC7447AHX1000NB | PowerPC microprocessor |

| MC7447AHX1167NB | PowerPC microprocessor |

| MC74F126J | 4-Bit Buffer/Driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC7445ARX1000LG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:RISC Microprocessor Hardware Specifications |

| MC7445ARX733LF | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:RISC Microprocessor Hardware Specifications |

| MC7445ARX733LG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:RISC Microprocessor Hardware Specifications |

| MC7445ARX867LF | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:RISC Microprocessor Hardware Specifications |

| MC7445ARX867LG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:RISC Microprocessor Hardware Specifications |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。