- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385574 > MCM20027IBMN (MOTOROLA INC) Color SXGA Digital Image Sensor 1280 x 1024 pixel progressive scan solid state image sensor with integrated CDS/PGA/ADC, digital programming, control PDF資料下載

參數(shù)資料

| 型號: | MCM20027IBMN |

| 廠商: | MOTOROLA INC |

| 元件分類: | 圖像傳感器 |

| 英文描述: | Color SXGA Digital Image Sensor 1280 x 1024 pixel progressive scan solid state image sensor with integrated CDS/PGA/ADC, digital programming, control |

| 中文描述: | IMAGE SENSOR-CMOS, 10fps, 0.20-2.80V, SQUARE, SURFACE MOUNT |

| 封裝: | CERAMIC, LCC-48 |

| 文件頁數(shù): | 48/74頁 |

| 文件大小: | 973K |

| 代理商: | MCM20027IBMN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

MOTOROLA

Revision 8.0 - 28 November 2001 : MCM20027

48

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

ImageMOS

SFRS mode. Please refer to

Figure 14, on page 20

for

a timing diagram of this mode.

The

sp

bit is used to define whether SOF is active high

or low. SOF is active high in default.

The

ve

bit is used to determine whether VCLK is output

at the beginning of all the rows including virtual frame

rows or for the WOI rows only. The default is WOI only.

The

vp

bit is used to define whether VCLK is active high

or low. VCLK is active high in default.

The

he

bit is used to determine whether HCLK is output

continuously or for the WOI pixels only. The default is

WOI only.

The

hp

bit is used to define whether HCLK is active high

or low. HCLK is active high in default.

The

hm

bit is used to define HCLK is toggled or wheth-

erwhether it is continuously output.

The

Sub-sample Control Register; Table 30

, is used to

define what pixels of the WOI are read and the method

they are read.

Using the

cm

bit, the user can sample the pixel array in

either monochrome or Bayer pattern color space. This

means that when sampling the rows or columns, the set

of pixels read will be gathered as individual pixels

(monochrome) or in color tiles of pixels (Bayer pattern).

The pixels will be read in monochrome mode in default.

The row sub sampling rate is defined by

rf

[1:0] while the

column sub sampling rate is defined by

cf

[1:0]. The pix-

el array is fully sampled in default.

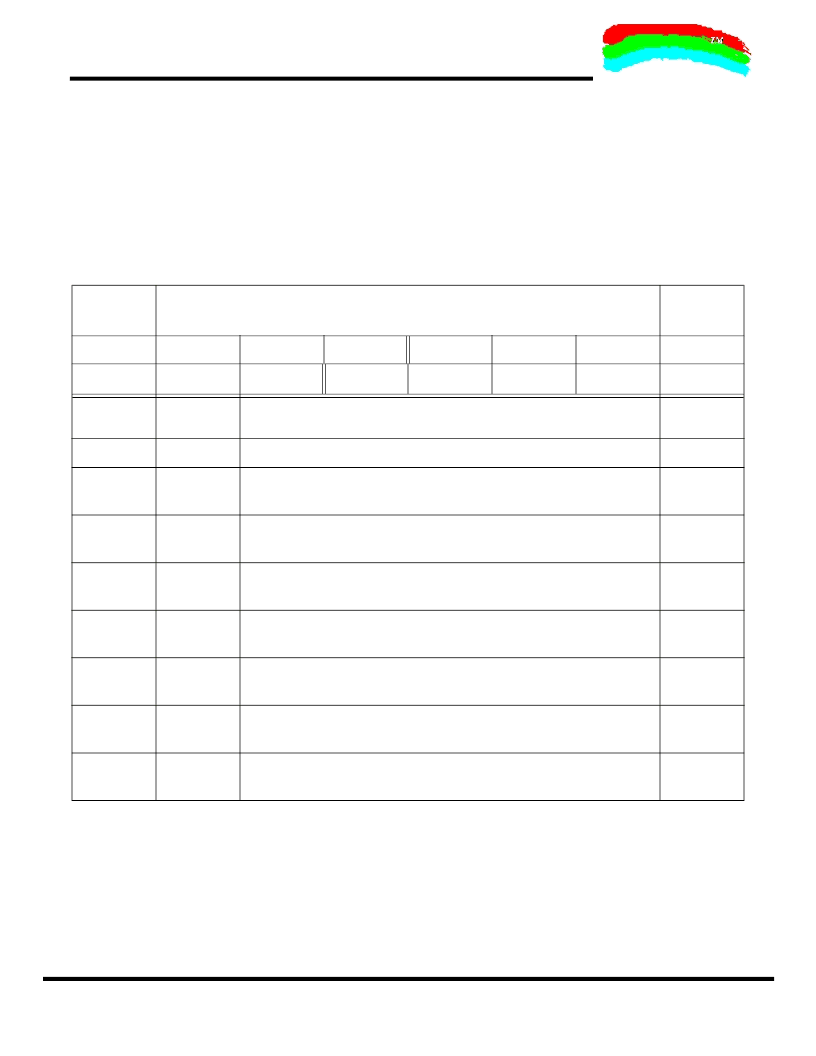

Address

40

h

Capture Mode Control

Default

2A

h

msb (7)

6

5

4

3

2

1

lsb (0)

FUO

cms

sp

ve

vp

he

hp

hm

Bit

Number

Function

Description

Reset

State

7

FUO

Factory Use Only

0

b

6

Capture

Mode

0

b

= Continuos Frame Rolling Shutter

1

b

= Single Frame Rolling Shutter

0

b

5

SOF

Phase

1

b

= SOF active high

0

b

= SOF active low

1

b

4

VCLK

Enable

1

b

= All virtual frame rows

0

b

= Window of Interest rows only

0

b

3

VCLK

Phase

1

b

= Active high

0

b

= Active low

1

b

2

HCLK

Enable

1

b

= Continuous

0

b

= Window of Interest Pixels only

0

b

1

HCLK

Phase

1

b

= Active high

0

b

= Active low

1

b

0

HCLK

Mode

1

b

= Continuous - envelope

0

b

= Toggles - like MCLK

0

b

Table 29. Capture Mode Control Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCP1252 | Low Noise, Positive-Regulated Charge Pump |

| MCP1253 | Low Noise, Positive-Regulated Charge Pump |

| MCP1525 | 2.5V AND 4.096V VOLTAGE REFERENCES |

| MCP1541 | 2.5V AND 4.096V VOLTAGE REFERENCES |

| MCP1630 | High-Speed, Microcontroller-Adaptable, Pulse Width Modulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM2012B221FBE | 制造商: 功能描述:Chip Common Mode Filter 制造商:undefined 功能描述:Chip Common Mode Filter |

| MCM2012B900GBE | 制造商:undefined 功能描述:Chip Common Mode Filter |

| MCM2016HN45 | 制造商:Motorola Inc 功能描述: |

| MCM2016HN55 | 制造商:Motorola Inc 功能描述: |

| MCM2114P30 | 制造商:Motorola Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。