- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371086 > MCM62Y308 (Motorola, Inc.) Synchronous Line Buffer:8K x 8 Bit Fast Static Dual Ported Memory PDF資料下載

參數(shù)資料

| 型號: | MCM62Y308 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Synchronous Line Buffer:8K x 8 Bit Fast Static Dual Ported Memory |

| 中文描述: | 同步線緩沖區(qū)器:8K × 8位快速靜態(tài)雙端口存儲器 |

| 文件頁數(shù): | 1/16頁 |

| 文件大小: | 257K |

| 代理商: | MCM62Y308 |

MCM62Y308

1

Motorola, Inc. 1994

Advance Information

Synchronous Line Buffer:

8K x 8 Bit Fast Static Dual

Ported Memory

With IEEE Standard 1149.1 Test Access Port

and Boundary–Scan (JTAG)

The MCM62Y308 is a synchronous, dual ported memory organized as 8,192

words of 8 bits each, fabricated using Motorola’s double–metal, double–poly,

0.65

μ

m CMOS process. It is intended for high speed video or other applications

which process data on a line–by–line basis. Through the use of a single clock and

port control inputs, separate read and write data ports provide simultaneous ac-

cess to a common memory array. Simultaneous read/write access to the same

address location is also allowed, with old data being read followed by a write of

the new data. This allows multiple devices to be cascaded with the output of one

directly driving the input of another. In this configuration the data stream can be

tapped at strategic interconnect points to perform various digital filtering functions.

Since there are no external address inputs, separate internal read and write

address counters are provided as a means of indexing the memory array. These

counters are preloaded and then selectively incremented or decremented by

asserting read enable (RE) and write enable (WE) inputs, allowing cycle to cycle

control. The address counters can be reloaded back to their initial values through the

use of the read reload (RR) and write reload (WR) control inputs. These inputs

initiate the transfer of address reload register values into the address counters which

index the memory array. When an address counter reaches 0000 it will roll over on

the next count. On the down count the roll over condition will cause the roll–over flag

(WRF or RRF) to assert high. On the up count these flags must be treated as don’t

cares. The roll–over flag outputs are cleared when their associated roll–over reset

pin is asserted low. The TDI input is used to write the reload registers using special

test access port instructions.

The read and write address counters are 16 bits long, and only 13 of the 16 bits

are required to index the 8K deep memory array. The remaining three bits are

used for depth expansion. These three bits are compared to the lower three bits

in the control register, and as long as they are equal that port (i.e., read or write)

will remain active. If the bits do not compare, the port will become inactive (i.e.,

for read outputs, high–z; for write inputs, disabled) however, the counter will

continue to count on the rising edge of K as long as the port enable signal (RE or

WE) is asserted. The TDI input is used to write the control register using special

test access port instructions.

The output enable Input can be programmed to be either synchronous or

asynchronous through the control register.

The MCM62Y308 is available in a 32 pin SOJ package.

8K x 8 Fast Access Static Memory Array

Single 5 V Power Supply — MCM62Y308–17:

±

5%

Synchronous, Simultaneous Read/Write Memory Access

50 MHz Maximum Clock Cycle Time, < 15 ns Read Access

Single Clock Operation

Separate Read/Write Address Counters with Reload Control

Separate Up/Down Counter Control for Both Read and Write

Separate Roll–Over Flag Outputs for Read and Write

Programmable Output Enable Control (Synchronous or Asynchronous)

Cascadable I/O Interface

IEEE Standard 1149.1 Test Port (JTAG)

Expand ID Register for Depth Expansion

High Board Density SOJ Package

This document contains information on a new product under development. Motorola reserves the right to change or discontinue this product without notice.

REV 2

5/95

Order this document

by MCM62Y308/D

SEMICONDUCTOR TECHNICAL DATA

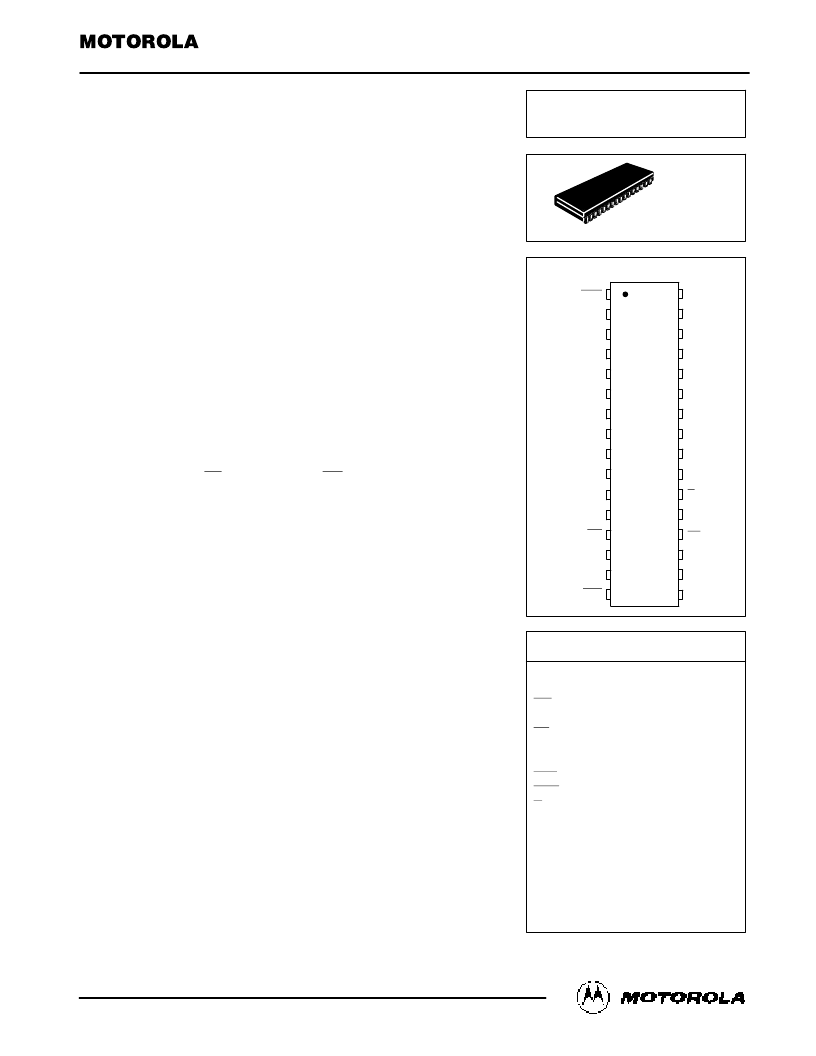

MCM62Y308

J PACKAGE

300 MIL SOJ

CASE 857–02

PIN ASSIGNMENT

5

4

3

2

1

10

9

8

7

6

11

12

13

14

20

21

22

23

24

25

26

19

27

28

18

17

D1

D4

D5

D6

D7

WE

D0

D3

TCK

TDI

WR

D2

VDD

K

Q3

Q4

Q5

Q6

Q7

TDO

RR

RE

TMS

VSS

Q1

Q2

G

Q0

PIN NAMES

K

WE

WR

RE

RR

RRF

WRF

RRR

WRR

G

D0 – D7

Q0 – Q7

TCK

TMS

TDI

TDO

VDD

VSS

Clock Input

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

Write Address Reload Input

. . . . . . . . . .

. . . . . . . . . . . . . . . . .

Read Address Reload Input

. . . . . . . . .

Read Roll–Over Flag Output

. . . . . . . .

Write Roll–Over Flag Output

. . . . . . .

Read Roll–Over Reset Input

. . . . . . . .

Write Roll–Over Reset Input

. . . . . . .

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

Write Enable Input

.Read Enable Input

Output Enable Input

Data Inputs

Data Outputs

Test Clock Input

Test Mode Select

Test Data Input

Test Data Output

+ 5 V Power Supply

Ground

32

1

15

16

29

30

31

32

WRR

RRR

RRF

WRF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM62Y308J17 | Synchronous Line Buffer:8K x 8 Bit Fast Static Dual Ported Memory |

| MCM6323A | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323AYJ10 | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323AYJ10R | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323AYJ12 | 64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM62Y308J17 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Synchronous Line Buffer:8K x 8 Bit Fast Static Dual Ported Memory |

| MCM6323A | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323ATS10 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323ATS10R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

| MCM6323ATS12 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 16 Bit 3.3 V Asynchronous Fast Static RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。