- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371090 > MCM6709ARJ7 (MOTOROLA INC) Replaced by PTH05060W : PDF資料下載

參數(shù)資料

| 型號: | MCM6709ARJ7 |

| 廠商: | MOTOROLA INC |

| 元件分類: | DRAM |

| 英文描述: | Replaced by PTH05060W : |

| 中文描述: | 64K X 4 STANDARD SRAM, 7 ns, PDSO28 |

| 封裝: | 0.300 INCH, PLASTIC, SOJ-28 |

| 文件頁數(shù): | 2/7頁 |

| 文件大小: | 102K |

| 代理商: | MCM6709ARJ7 |

MCM6709BR

2

MOTOROLA FAST SRAM

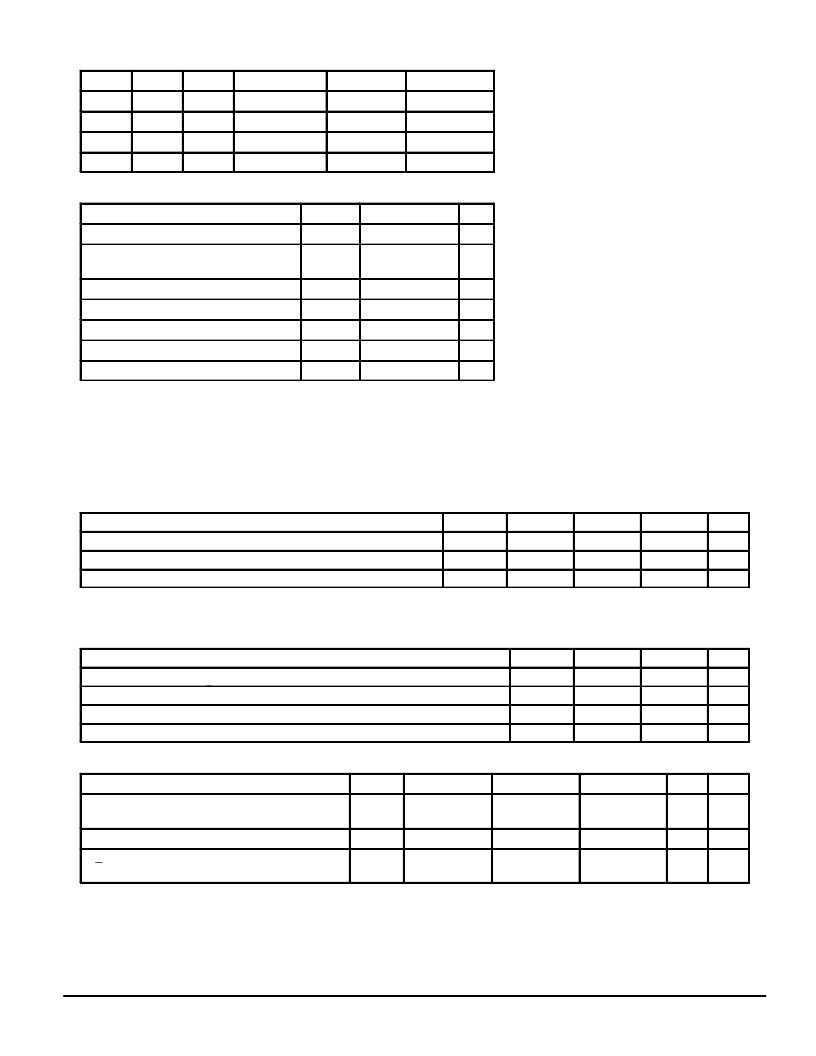

TRUTH TABLE

(X = Don’t Care)

E

G

W

Mode

Output

Cycle

H

X

X

Not Selected

High–Z

—

L

H

H

Read

High–Z

—

L

L

H

Read

Dout

Din

Read Cycle

L

X

L

Write

Write Cycle

ABSOLUTE MAXIMUM RATINGS

(See Note)

Rating

Symbol

Value

Unit

Power Supply Voltage

VCC

Vin, Vout

– 0.5 to + 7.0

V

Voltage Relative to VSS for Any Pin

Except VCC

– 0.5 to VCC + 0.5

V

Output Current (per I/O)

Iout

PD

Tbias

TA

Tstg

±

30

mA

Power Dissipation

2.0

W

Temperature Under Bias

– 10 to + 85

°

C

Operating Temperature

0 to + 70

°

C

Storage Temperature — Plastic

– 55 to + 125

°

C

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are

exceeded. Functional operation should be restricted to RECOMMENDED OPER-

ATING CONDITIONS. Exposure to higher than recommended voltages for

extended periods of time could affect device reliability.

DC OPERATING CONDITIONS AND CHARACTERISTICS

(VCC = 5.0 V

±

10%, TA = 0 to 70

°

C, Unless Otherwise Noted)

RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Min

Typ

Max

Unit

Supply Voltage (Operating Voltage Range)

VCC

VIH

VIL

4.5

5.0

5.5

V

Input High Voltage

2.2

—

VCC + 0.3*

0.8

V

Input Low Voltage

*VIH (max) = VCC + 0.3 V dc; VIH (max) = VCC + 2.0 V ac (pulse width

≤

2.0 ns) or I

≤

30.0 mA.

** VIL (min) = – 0.5 V dc @ 30.0 mA; VIL (min) = – 2.0 V ac (pulse width

≤

2.0 ns) or I

≤

30.0 mA.

– 0.5**

—

V

DC CHARACTERISTICS

Parameter

Symbol

Min

Max

Unit

Input Leakage Current (All Inputs, Vin = 0 to VCC)

Output Leakage Current (E = VIH, Vout = 0 to VCC)

Output High Voltage (IOH = – 4.0 mA)

Output Low Voltage (IOL = 8.0 mA)

Ilkg(I)

Ilkg(O)

VOH

VOL

—

±

1.0

±

1.0

μ

A

μ

A

—

2.4

—

V

—

0.4

V

POWER SUPPLY CURRENTS

Parameter

Symbol

MCM6709BR–6

MCM6709BR–7

MCM6709BR–8

Unit

Notes

AC Active Supply Current (Iout = 0 mA, VCC = max,

f = fmax)

ICCA

215

205

195

mA

1, 2, 3

AC Standby Current (E = VIH, VCC = max, f = fmax)

CMOS Standby Current (VCC = max, f = 0 MHz,

E

≥

VCC – 0.2 V, Vin

≤

VSS, or

≥

VCC – 0.2 V)

NOTES:

1. Reference AC Operating Conditions and Characteristics for input and timing (VIH/VIL, tr/tf, pulse level 0 to 3.0 V, VIH = 3.0 V).

2. All addresses transition simultaneously low (LSB) and then high (MSB).

3. Data states are all zero.

ISB1

ISB2

95

85

75

mA

1, 2, 3

20

20

20

mA

This device contains circuitry to protect the

inputs against damage due to high static volt-

ages or electric fields; however, it is advised

that normal precautions be taken to avoid appli-

cation of any voltage higher than maximum

rated voltages to this high–impedance circuit.

This BiCMOS memory circuit has been de-

signed to meet the dc and ac specifications

shown in the tables, after thermal equilibrium

has been established. The circuit is in a test

socket or mounted on a printed circuit board

and transverse air flow of at least 500 linear feet

per minute is maintained.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM6709BR | 64K x 4 Bit Static RAM |

| MCM6709ARJ7R2 | 64K x 4 Bit Static RAM |

| MCM6709RJ7R2 | 64K x 4 Bit Static RAM |

| MCM6709RJ8R2 | 64K x 4 Bit Static RAM |

| MCM6709RJ6R2 | 64K x 4 Bit Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM6709ARJ7R2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709B | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709BJ10 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709BJ10R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

| MCM6709BJ12 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:64K x 4 Bit Static RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。