- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371091 > MCM67C618AFN5 (MOTOROLA INC) 64K x 18 Bit BurstRAM Synchronous Fast Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | MCM67C618AFN5 |

| 廠商: | MOTOROLA INC |

| 元件分類(lèi): | SRAM |

| 英文描述: | 64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| 中文描述: | 64K X 18 CACHE SRAM, PQCC52 |

| 封裝: | PLASTIC, LCC-52 |

| 文件頁(yè)數(shù): | 2/12頁(yè) |

| 文件大小: | 158K |

| 代理商: | MCM67C618AFN5 |

MCM67C618A

2

MOTOROLA FAST SRAM

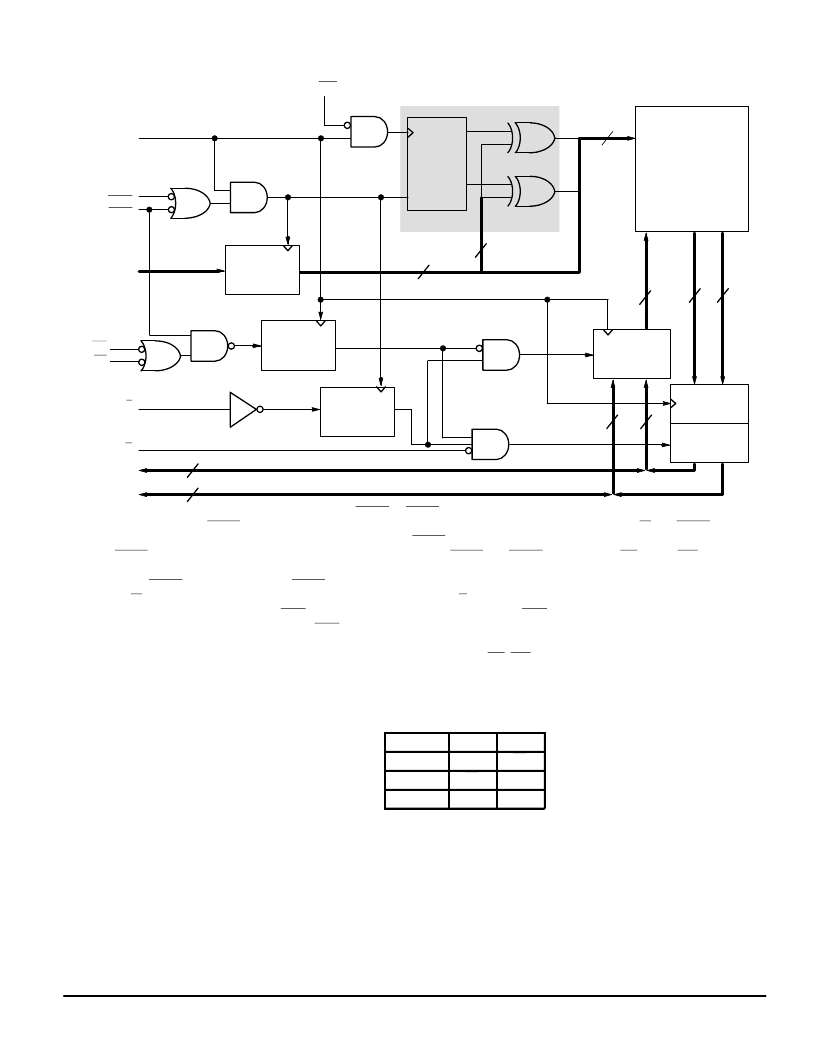

BLOCK DIAGRAM

(See Note)

DQ0 – DQ8

CLR

Q0

Q1

A0

A1

K

ADSC

ADSP

A0 – A15

E

G

ADDRESS

REGISTER

WRITE

REGISTER

ENABLE

REGISTER

DATA–IN

REGISTERS

OUTPUT

BUFFER

64K x 18

MEMORY

ARRAY

ADV

BURST LOGIC

INTERNAL

ADDRESS

A0

′

16

9

18

16

2

A2 – A15

A1 – A0

DQ9 – DQ17

9

9

9

9

9

BINARY

COUNTER

DATA–OUT

REGISTERS

UW

LW

NOTE:

All registers are positive–edge triggered. The ADSC or ADSP signals control the duration of the burst and the start of the

next burst. When ADSP is sampled low, any ongoing burst is interrupted and a read (independent of W and ADSC) is per-

formed using the new external address. Alternatively, an ADSP–initiated two cycle WRITE can be performed by asserting

ADSP and a valid address on the first cycle, then negating both ADSP and ADSC and asserting LW and/or UW with valid

data on the second cycle (see Single Write cycle in WRITE CYCLES timing diagram).

When ADSC is sampled low (and ADSP is sampled high), any ongoing burst is interrupted and a read or write (dependent

on W) is performed using the new external address. Chip enable (E) is sampled only when a new base address is loaded.

After the first cycle of the burst, ADV controls subsequent burst cycles. When ADV is sampled low, the internal address is

advanced prior to the operation. When ADV is sampled high, the internal address is not advanced, thus inserting a wait state

into the burst sequence accesses. Upon completion of a burst, the address will wrap around to its initial state. See

BURST

SEQUENCE TABLE

. Write refers to either or both byte write enables (LW, UW).

BURST SEQUENCE TABLE

(See Note)

External Address

A15 – A2

A1

A0

1st Burst Address

A15 – A2

A1

A0

2nd Burst Address

A15 – A2

A1

A0

3rd Burst Address

A15 – A2

A1

A0

NOTE: The burst wraps around to its initial state upon completion.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM67C618AFN7 | 64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67C618A | 64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67H618AFN10 | 64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67H618A | 64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67H618AFN12 | LJT 8C 8#16 SKT WALL RECP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM67C618AFN7 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67C618B | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67C618BFN5 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67C618BFN7 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

| MCM67C618FN6 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:64K x 18 Bit BurstRAM Synchronous Fast Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。