- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371107 > MH4V6445BXJJ-6 (Mitsubishi Electric Corporation) HYPER PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | MH4V6445BXJJ-6 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | HYPER PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

| 中文描述: | 超頁模式268435456位(4194304字,64位)動(dòng)態(tài)隨機(jī)存儲(chǔ)器 |

| 文件頁數(shù): | 8/26頁 |

| 文件大?。?/td> | 152K |

| 代理商: | MH4V6445BXJJ-6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

MH4V6445BXJJ-5,-6,-5S,-6S

HYPER PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM

MITSUBISHI

ELECTRIC

( / 26 )

8

MITSUBISHI LSIs

Preliminary

Some of contents are subject

to change without notice.

MIT-DS-0233-0.0

24/Jul./1998

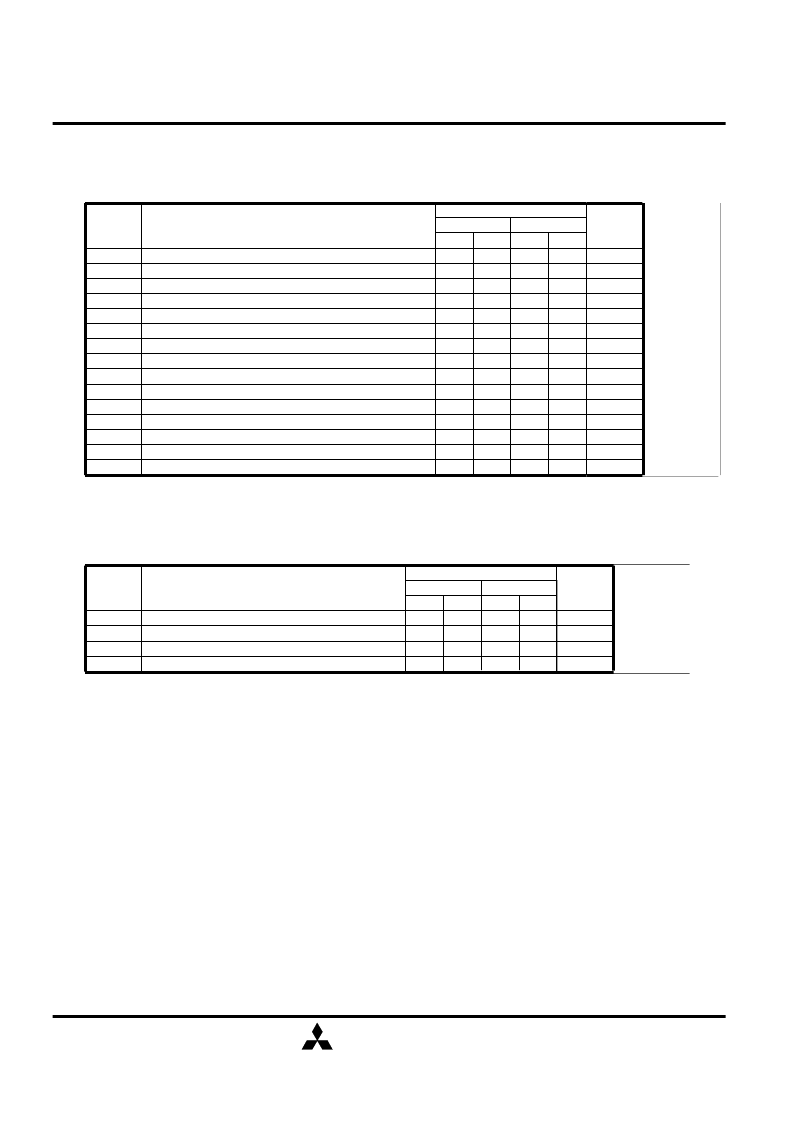

Hyper Page Mode Cycle (Read, Early Write, Read -Write, Read-Modify-Write Cycle,

Read Write Mix Cycle,Hi-Z control by /OE or /WE)

(Note 25)

Note 25: All previously specified timing requirements and switching characteristics are applicable to their respective Hyper page mode cycle.

26: tRAS(min) is specified as two cycles of /CAS input are performed.

27: tCP(max) is specified as a reference point only.If tCP

≥

tCP(max),access time is controlled exclusively by tCAC.

Limits

Parameter

Symbol

Min

25

66

Max

(Note26)

(Note27)

16

100000

/CAS before /RAS Refresh Cycle

(Note 28)

Limits

Parameter

Symbol

Unit

Min

Max

Note 28: Eight or more /CAS before /RAS cycles instead of eight /RAS cycles are necessary for proper operation of /CAS before /RAS

refresh mode.

-6,-6S

-6,-6S

Min

30

79

Max

16

100000

-7,-7S

Min

Max

-7,-7S

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

tHPC

tHPRWC

tRAS

tCP

tCPRH

tCPWD

tCHOL

tOEPE

tWPE

tHCWD

tHAWD

tHPWD

tHCOD

tHAOD

tHPOD

Hyper page mode read/write cycle time

Hyper page mode read write/read modify write cycle time

/RAS low pulse width for read write cycle

/CAS high pulse width

/RAS hold time after /CAS precharge

Delay time, /CAS precharge to /W low

Hold time to maintain the data Hi-Z until /CAS access

/OE Pulse Width (Hi-Z control)

/W Pulse Width (Hi-Z control)

Delay time, /CAS low to /W low after read

Delay time, Address to /W low after read

Delay time, /CAS precharge to /W low after read

Delay time, /CAS low to /OE high after read

Delay time, Address to /OE high after read

Delay time, /CAS prechargeto /OE high after read

33

50

7

7

7

32

47

50

15

30

33

77

10

40

62

7

7

7

42

72

82

20

35

40

92

10

(Note24)

ns

ns

ns

ns

tCSR

tCHR

tRSR

tRHR

/CAS setup time before /RAS low

/CAS hold time after /RAS low

Read setup time before /RAS low

Read hold time after /RAS low

10

10

5

5

ns

ns

ns

ns

15

5

15

-5,-5S

Min

20

55

Max

13

100000

28

43

7

7

7

28

40

43

13

25

28

65

8

-5,-5S

Min

5

Max

10

10

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

10

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MH4V6445BXJJ-6S | HYPER PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

| MH64D72KLG-10 | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64D72KLG-75 | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64D72KLH-10 | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH64D72KLH-75 | 4,831,838,208-BIT (67,108,864-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MH4V6445BXJJ-6S | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:HYPER PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

| MH4V644AWXJ-5 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:FAST PAGE MODE 268435456 - BIT ( 4194304 - WORD BY 64 - BIT ) DYNAMIC RAM |

| MH4V644AWXJ-6 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:FAST PAGE MODE 268435456 - BIT ( 4194304 - WORD BY 64 - BIT ) DYNAMIC RAM |

| MH4V644AXJJ | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

| MH4V644AXJJ-5 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。