- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄26831 > ML6510CQ-80 (FAIRCHILD SEMICONDUCTOR CORP) PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC44 PDF資料下載

參數(shù)資料

| 型號: | ML6510CQ-80 |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 時鐘及定時 |

| 英文描述: | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 14/18頁 |

| 文件大小: | 150K |

| 代理商: | ML6510CQ-80 |

ML6510

REV. 1.0 10/25/2000

5

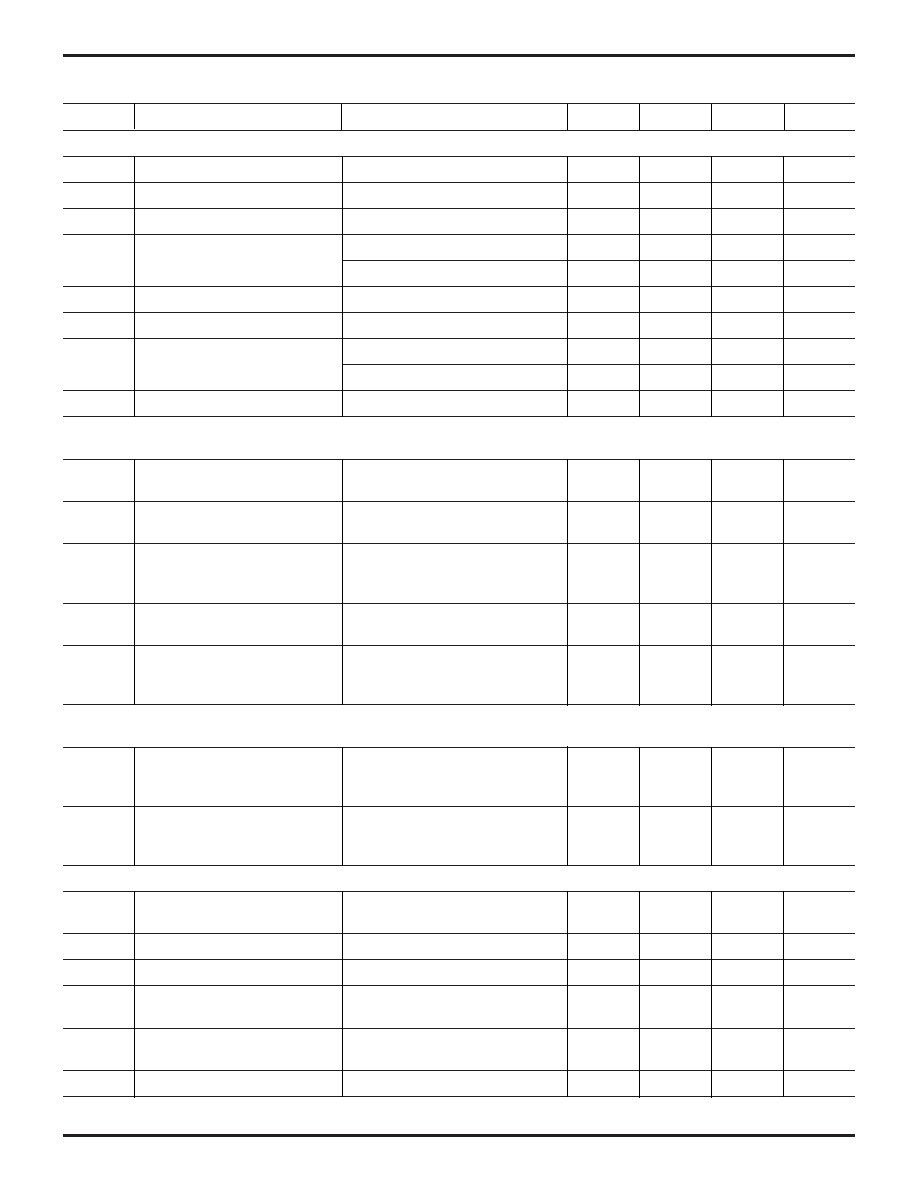

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNIT

AC Characteristics rise time, fall time and duty cycle are measured for a generic load; (see Load Conditions section).

tR

Rise time, LOAD [0-7] output

0.8

2.0V, 80MHz

150

1500

ps

tF

Fall time, LOAD [0-7] output

2.0

0.8V, 80MHz

150

1500

ps

fIN

Input frequency, CLKIN pin

10

80

MHz

fOUT

Output frequency , CLK [0-7]

ML6510-80

10

80

MHz

output

ML6510-130 (Note 2)

10

130

MHz

fVCO

PLL VCO operating frequency

80

160

MHz

DC

Output duty cycle

Measured at device load, at 1.5V

40

60

%

tJITTER

Output jitter

Cycle-to-cycle

75

ps

Peak-to-peak

150

ps

tLOCK

PLL and deskew lock time

After programming is complete

11

ms

Skew Characteristics

All skew measurements are made at the load, at 1.5V threshold each output load can vary independently

within the specified range for a generic load (see Load Conditions section).

tSKEWR

Output to output rising

500

ps

edge skew, all clocks

tSKEWF

Output to output

Output clock frequency 50MHz

1.5

ns

falling edge skew

tSKEWIO

CLKIN input to any

N = M = 0

600

ps

LOAD [0-7] output

rising edge skew

N 2, M 2

1.25

ns

tRANGE

Round trip delay CLKX to FBX

Output frequency < 50MHz

0

10

ns

pin; output CLK period = tCLK

Output frequency 50MHz

0

tCLK/2

tSKEWB

Output-to-output rising

Providing first (see LOAD

250

ps

edge skew, between matched

conditions) order matching

loads

order matching between outputs

Part-To-Part Skew Characteristics

Skew measured at the loads, at 1.5V threshold. Reference clock output pins drive clock

input pins of another ML6510.

tPP1

Total load-to-load skew between

Slave chip CS = 1, CM = 1 and

1

ns

multiple chips interfaced with

N = 0, M = 0; RCLK outputs to

reference clock pins.

CLKIN inputs distance less than 2"

tPP2

Total load-to-load skew between

Slave chip CS = 1, CM = 1 and

1

ns

multiple chips interfaced with

N 2, M 2; RCLK outputs to

reference clock pins.

CLKIN inputs distance less than 2"

Programming Timing Characteristics

tRESET

RESET assertion pulse

50

ns

width

tA1

AUX mode MCLK high time

2000

ns

tA2

AUX mode MCLK low time

2000

ns

tA3

AUX mode MDOUT data

10

ns

hold time

tA4

AUX mode MDOUT data

10

ns

setup time

tA5

AUX mode MCLK period

5000

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML6516241CR | BICMOS SERIES, QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| ML6516244CT | QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| ML6516444CR | BICMOS SERIES, 16-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| ML65244CS | DUAL 4-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| ML65245CK | TTL/H/L SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML6516244 | 制造商:MICRO-LINEAR 制造商全稱:MICRO-LINEAR 功能描述:16-Bit Buffer/Line Driver with 3-State Outputs |

| ML6516244CR | 制造商:MICRO-LINEAR 制造商全稱:MICRO-LINEAR 功能描述:16-Bit Buffer/Line Driver with 3-State Outputs |

| ML6516244CT | 制造商:MICRO-LINEAR 制造商全稱:MICRO-LINEAR 功能描述:16-Bit Buffer/Line Driver with 3-State Outputs |

| ML6518 | 制造商:MICRO-LINEAR 制造商全稱:MICRO-LINEAR 功能描述:18 Line Hot-Insertable Active SCSI Terminator |

| ML6518CH | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。