- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45361 > MPC8347ECZQAJDB (FREESCALE SEMICONDUCTOR INC) 32-BIT, 533 MHz, MICROPROCESSOR, PBGA620 PDF資料下載

參數(shù)資料

| 型號: | MPC8347ECZQAJDB |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 533 MHz, MICROPROCESSOR, PBGA620 |

| 封裝: | 29 X 29 MM, 2.46 MM HEIGHT, 1 MM PITCH, PLASTIC, BGA-620 |

| 文件頁數(shù): | 6/98頁 |

| 文件大?。?/td> | 1084K |

| 代理商: | MPC8347ECZQAJDB |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications, Rev. 11

14

Freescale Semiconductor

RESET Initialization

5.2

RESET AC Electrical Characteristics

Table 10 provides the reset initialization AC timing specifications of the MPC8347EA.

Output low voltage

VOL

IOL = 3.2 mA

—

0.4

V

Notes:

1. This table applies for pins PORESET, HRESET, SRESET, and QUIESCE.

2. HRESET and SRESET are open drain pins, thus VOH is not relevant for those pins.

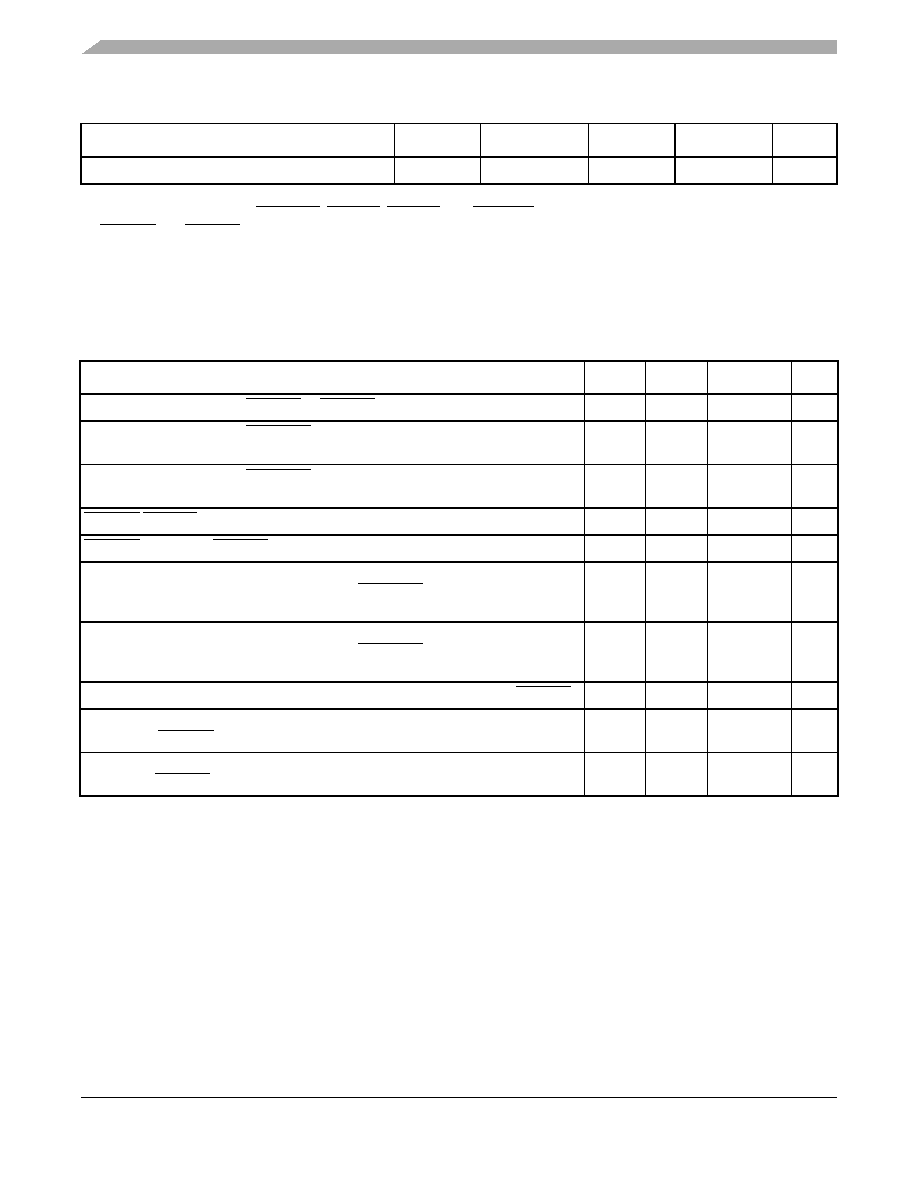

Table 10. RESET Initialization Timing Specifications

Parameter

Min

Max

Unit

Notes

Required assertion time of HRESET or SRESET (input) to activate reset flow

32

—

tPCI_SYNC_IN

1

Required assertion time of PORESET with stable clock applied to CLKIN when the

MPC8347EA is in PCI host mode

32

—

tCLKIN

2

Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN

when the MPC8347EA is in PCI agent mode

32

—

tPCI_SYNC_IN

1

HRESET/SRESET assertion (output)

512

—

tPCI_SYNC_IN

1

HRESET negation to SRESET negation (output)

16

—

tPCI_SYNC_IN

1

Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:2] and

CFG_CLKIN_DIV) with respect to negation of PORESET when the MPC8347EA is

in PCI host mode

4—

tCLKIN

2

Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:2] and

CFG_CLKIN_DIV) with respect to negation of PORESET when the MPC8347EA is

in PCI agent mode

4—

tPCI_SYNC_IN

1

Input hold time for POR configuration signals with respect to negation of HRESET

0—

ns

—

Time for the MPC8347EA to turn off POR configuration signals with respect to the

assertion of HRESET

—4

ns

3

Time for the MPC8347EA to turn on POR configuration signals with respect to the

negation of HRESET

1—

tPCI_SYNC_IN

1, 3

Notes:

1. tPCI_SYNC_IN is the clock period of the input clock applied to PCI_SYNC_IN. In PCI host mode, the primary clock is applied

to the CLKIN input, and PCI_SYNC_IN period depends on the value of CFG_CLKIN_DIV. See the MPC8349EA

PowerQUICC II Pro Integrated Host Processor Family Reference Manual.

2. tCLKIN is the clock period of the input clock applied to CLKIN. It is valid only in PCI host mode. See the MPC8349EA

PowerQUICC II Pro Integrated Host Processor Family Reference Manual.

3. POR configuration signals consist of CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV.

Table 9. RESET Pins DC Electrical Characteristics1 (continued)

Parameter

Symbol

Condition

Min

Max

Unit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8347CVVAJDB | 32-BIT, 533 MHz, MICROPROCESSOR, PBGA672 |

| MPC8347ZQALFB | 32-BIT, 667 MHz, MICROPROCESSOR, PBGA620 |

| MPC8347CVVALDB | 32-BIT, 667 MHz, MICROPROCESSOR, PBGA672 |

| MPC8347EZQAJFB | 32-BIT, 533 MHz, MICROPROCESSOR, PBGA620 |

| MPC8347EZUADDB | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA672 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8347ECZQAJFB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECZQALDB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECZQALFB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECZUADDB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECZUADFB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。