- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25637 > MQ80C52EXXX-36/883D (ATMEL CORP) 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MQ80C52EXXX-36/883D |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQFP44 |

| 封裝: | CERAMIC, QFP-44 |

| 文件頁數(shù): | 36/141頁 |

| 文件大小: | 7628K |

| 代理商: | MQ80C52EXXX-36/883D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁

215

8021G–AVR–03/11

ATmega329P/3290P

If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read

ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the Data

Registers belongs to the same conversion. Once ADCL is read, ADC access to Data Registers

is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is

read, neither register is updated and the result from the conversion is lost. When ADCH is read,

ADC access to the ADCH and ADCL Registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC

access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt

will trigger even if the result is lost.

22.4

Starting a Conversion

A single conversion is started by writing a logical one to the ADC Start Conversion bit, ADSC.

This bit stays high as long as the conversion is in progress and will be cleared by hardware

when the conversion is completed. If a different data channel is selected while a conversion is in

progress, the ADC will finish the current conversion before performing the channel change.

Alternatively, a conversion can be triggered automatically by various sources. Auto Triggering is

enabled by setting the ADC Auto Trigger Enable bit, ADATE in ADCSRA. The trigger source is

selected by setting the ADC Trigger Select bits, ADTS in ADCSRB (See description of the ADTS

bits for a list of the trigger sources). When a positive edge occurs on the selected trigger signal,

the ADC prescaler is reset and a conversion is started. This provides a method of starting con-

versions at fixed intervals. If the trigger signal still is set when the conversion completes, a new

conversion will not be started. If another positive edge occurs on the trigger signal during con-

version, the edge will be ignored. Note that an Interrupt Flag will be set even if the specific

interrupt is disabled or the Global Interrupt Enable bit in SREG is cleared. A conversion can thus

be triggered without causing an interrupt. However, the Interrupt Flag must be cleared in order to

trigger a new conversion at the next interrupt event.

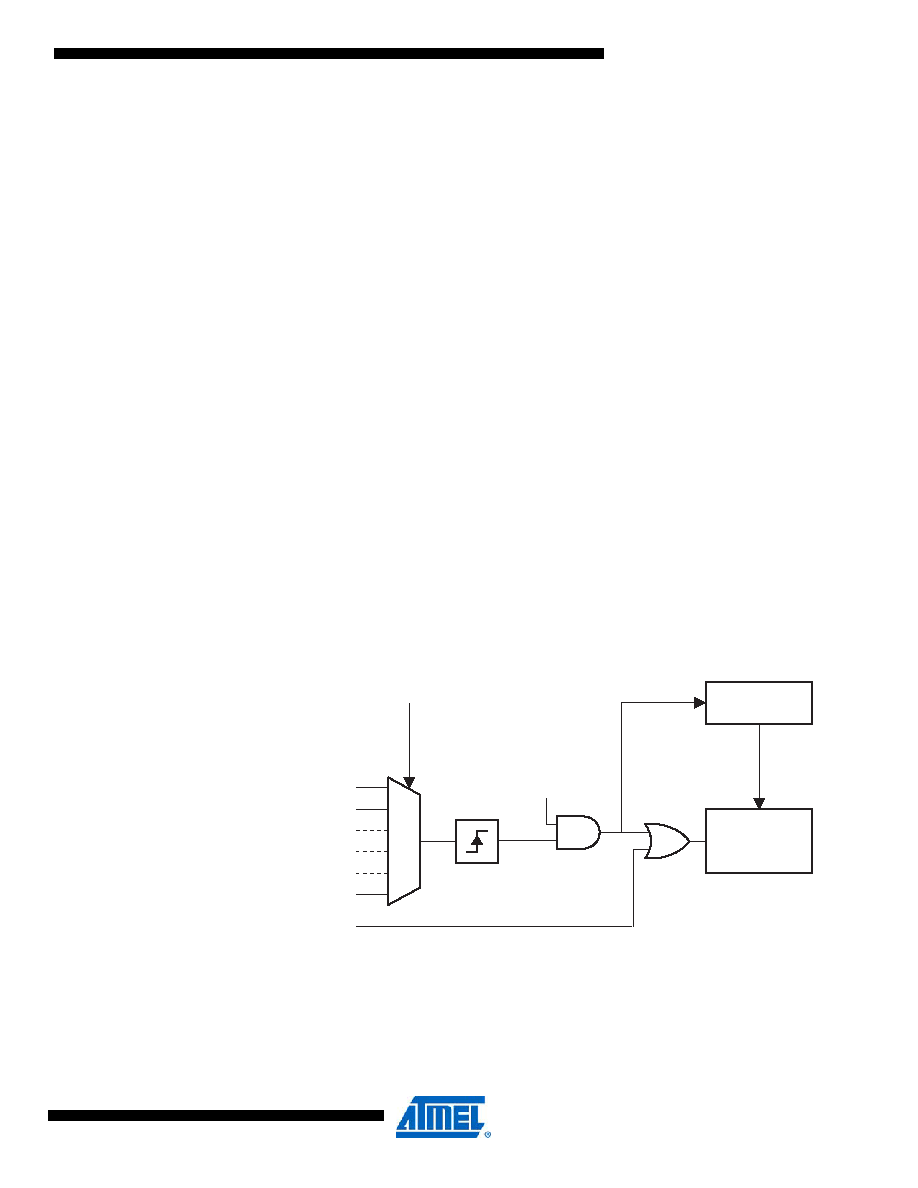

Figure 22-2. ADC Auto Trigger Logic

Using the ADC Interrupt Flag as a trigger source makes the ADC start a new conversion as soon

as the ongoing conversion has finished. The ADC then operates in Free Running mode, con-

stantly sampling and updating the ADC Data Register. The first conversion must be started by

writing a logical one to the ADSC bit in ADCSRA. In this mode the ADC will perform successive

conversions independently of whether the ADC Interrupt Flag, ADIF is cleared or not.

ADSC

ADIF

SOURCE 1

SOURCE n

ADTS[2:0]

CONVERSION

LOGIC

PRESCALER

START

CLK

ADC

.

EDGE

DETECTOR

ADATE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MD83C154CXXX-16P883D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MR83C154CXXX-25P883R | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| MR83C154XXX-25/883D | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| MD80C32E-16/883 | 8-BIT, 16 MHz, MICROCONTROLLER, CDIP40 |

| MC80C52EXXX-25/883:D | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MQ82370-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ8238020 | 制造商:Intel 功能描述:CONTROLLER: OTHER |

| MQ82380-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ82380-20/R | 制造商:Rochester Electronics LLC 功能描述: |

| MQ82592 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。