- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25639 > MS80C51-12D (ATMEL CORP) 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC44 PDF資料下載

參數(shù)資料

| 型號: | MS80C51-12D |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 56/80頁 |

| 文件大小: | 5152K |

| 代理商: | MS80C51-12D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當(dāng)前第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

256

XMEGA A [MANUAL]

8077I–AVR–11/2012

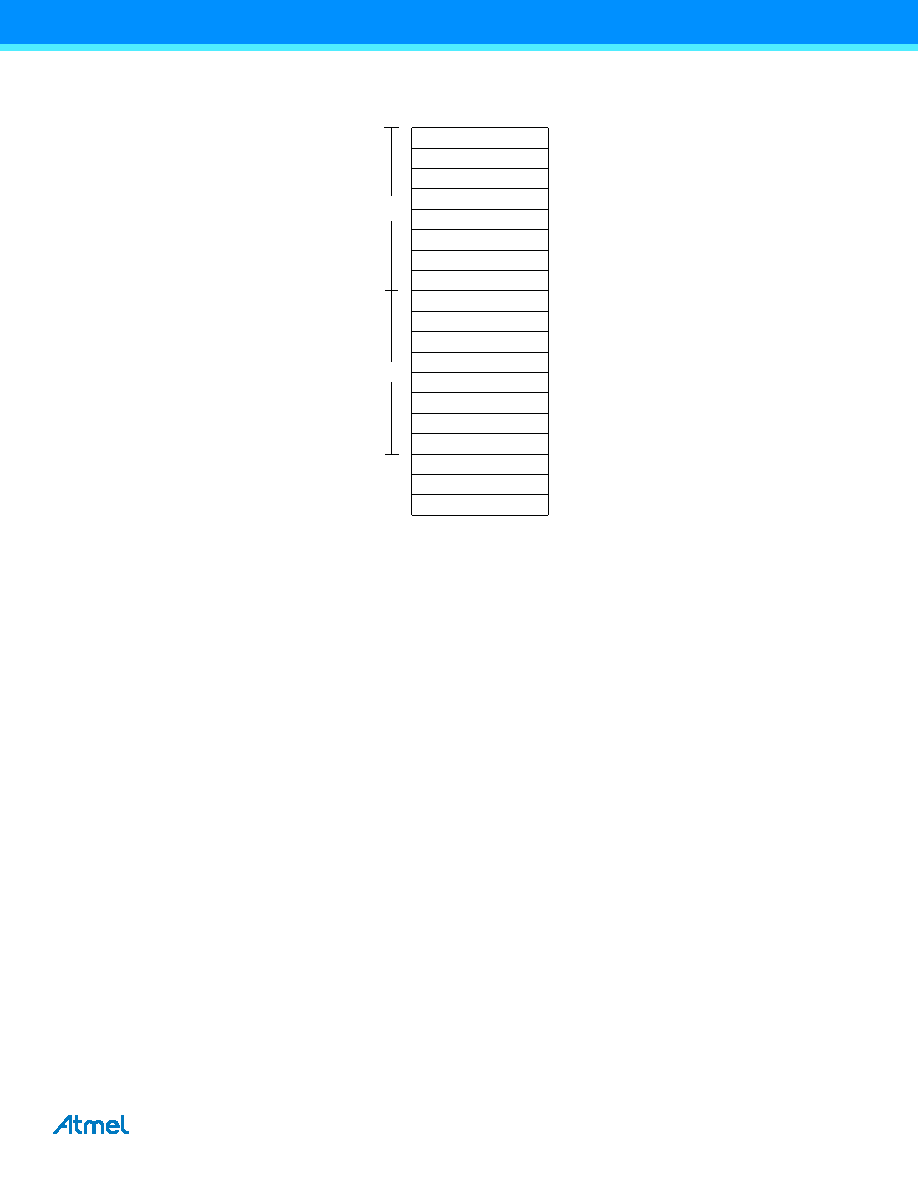

Figure 23-1. Register file usage during DES encryption/decryption.

Executing one DES instruction performs one round in the DES algorithm. Sixteen rounds must be executed in increasing

order to form the correct DES ciphertext or plaintext. Intermediate results are stored in the register file (R0-R15) after

each DES instruction. After sixteen rounds, the key is located in R8-R16 and the encrypted/decrypted ciphertext/plaintext

is located in R0-R7. The instruction's operand (K) determines which round is executed, and the half carry flag (H) in the

CPU status register determines whether encryption or decryption is performed. If the half carry flag is set, decryption is

performed, and if the flag is cleared, encryption is performed.

For more details on the DES instruction, refer to the AVR instruction set manual.

23.4

AES Crypto Module

The AES crypto module performs encryption and decryption according to the Advanced Encryption Standard (FIPS-197).

The 128-bit key block and 128-bit data block (plaintext or ciphertext) must be loaded into the key and state memories in

the AES crypto module. This is done by writing the AES KEY register and STATE register sequentially with 16 bytes.

It is software selectable whether the module should perform encryption or decryption. It is also possible to enable XOR

mode, where all new data loaded to the state key is XORed with the current data in the state memory.

The AES module uses 375 clock cycles before the encrypted/decrypted plaintext/ciphertext is available for readout in the

state memory.

The following setup and use procedure is recommended:

1.

Enable the AES interrupt (optional).

2.

Select the AES direction to encryption or decryption.

3.

Load the key data block into the AES key memory.

4.

Load the data block into the AES state memory.

5.

Start the encryption/decryption operation.

If more than one block is to be encrypted or decrypted, repeat the procedure from step 3.

When the encryption/decryption procedure is complete, the AES interrupt flag is set and an optional interrupt is

generated.

Register File

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

...

R31

data0

data1

data2

data3

data4

data5

data6

data7

key0

key1

key2

key3

key4

key5

key6

key7

data

key

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT80C51T-16R | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| MD80C32E-20SC | 8-BIT, 20 MHz, MICROCONTROLLER, CDIP40 |

| MC80C52XXX-16SHXXX | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52EXXX-20 | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52CXXX-12SHXXX | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MS8100 | 制造商:MCC 制造商全稱:Micro Commercial Components 功能描述:8 Amp Schottky Barrier Rectifier 20 to 100 Volts |

| MS8100.D | 制造商:Colibrys SA 功能描述:MEMS CAPACITIVE ACCELEROMETERS - Trays |

| MS8104160 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:(262,214-word x 8-Bits) x 2 Dual FIFO |

| MS8104160A | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Dual FIFO (262,214 Words 】 8 Bits) 】 2 |

| MS8104160A-XXTB | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Dual FIFO (262,214 Words 】 8 Bits) 】 2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。