- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8256SVT1000B (FREESCALE SEMICONDUCTOR INC) 0-BIT, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8256SVT1000B |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 0-BIT, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCBGA-783 |

| 文件頁數(shù): | 50/68頁 |

| 文件大小: | 910K |

| 代理商: | MSC8256SVT1000B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

MSC8256 Six-Core Digital Signal Processor Data Sheet, Rev. 3

Hardware Design Considerations

Freescale Semiconductor

54

3.1.2

Power-On Ramp Time

This section describes the AC electrical specification for the power-on ramp rate requirements for all voltage supplies (including

GVDD/SXPVDD/SXCVDD/QVDD/GVDD/NVDD, all VDD supplies, MVREF, and all AVDD supplies). Controlling the

power-on ramp time is required to avoid falsely triggering the ESD circuitry. Table 39 defines the power supply ramp time

specification.

3.1.3

Power Supply Guidelines

Use the following guidelines for power-up sequencing:

Couple M3VDD with the VDD power rail using an extremely low impedance path.

Couple inputs PLL1_AVDD, PLL2_AVDD and PLL3_AVDD with the VDD power rail using an RC filter (see Figure

There is no dependency in power-on/power-off sequence between the GVDD1, GVDD2, NVDD, and QVDD power

rails.

Couple inputs M1VREF and M2VREF with the GVDD1 and GVDD2 power rails, respectively. They should rise at

the same time as or after their respective power rail.

There is no dependency between RapidIO supplies: SXCVDD1, SXCVDD2, SXPVDD1 and SXPVDD2 and other

MSC8256 supplies in the power-on/power-off sequence

Couple inputs SR1_PLL_AVDD and SR2_PLL_AVDD with SXCVDD1 and SXCVDD2 power rails, respectively,

using an RC filter (see Figure 38).

External voltage applied to any input line must not exceed the I/O supply voltage related to this line by more than 0.6 V at any

time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for

configuration purposes. This is an acceptable exception to the rule during start-up. However, each such input can draw up to

80 mA per input pin per MSC8256 device in the system during power-up. An assertion of the inputs to the high voltage level

before power-up should be with slew rate less than 4 V/ns.

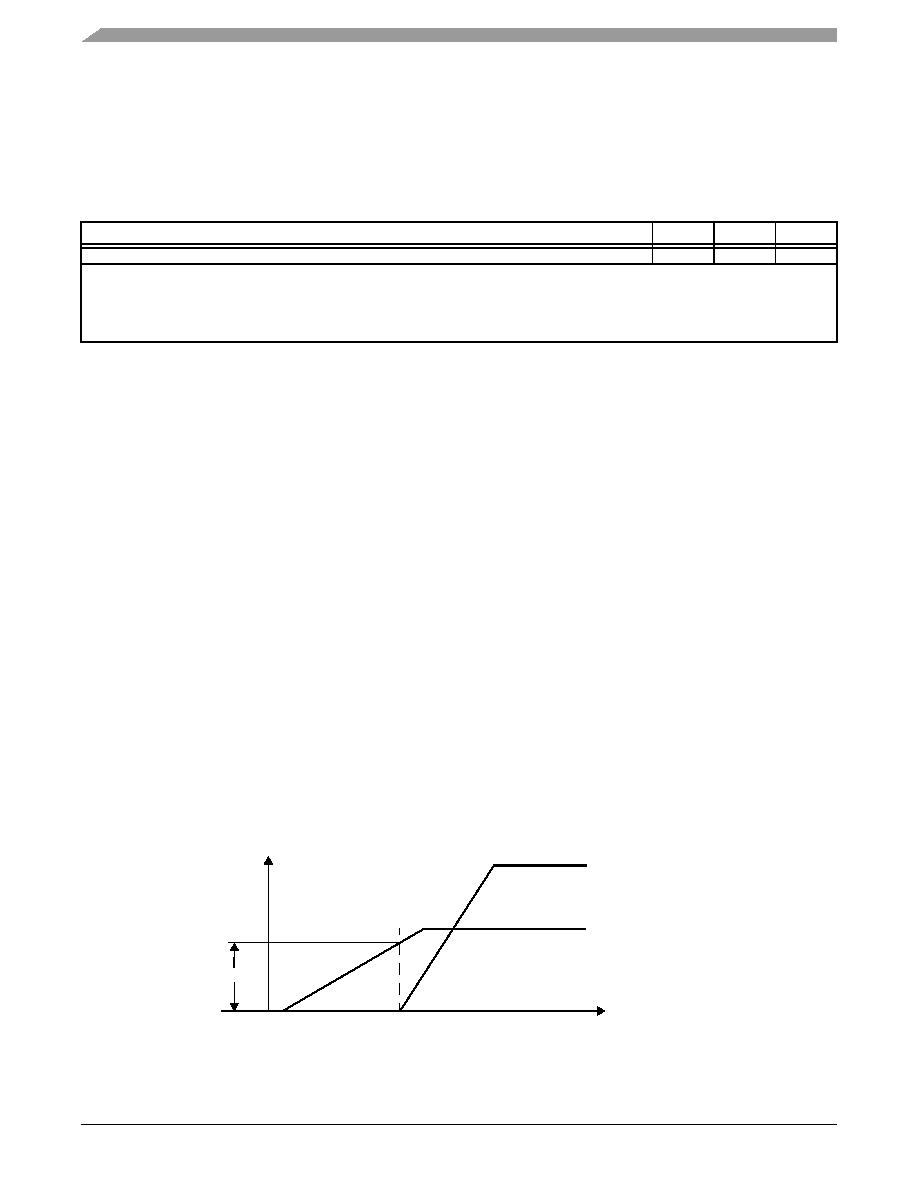

The device power rails should rise in the following sequence:

1.

VDD (and all coupled supplies)

2.

After the above rails rise to 90% of their nominal voltage, the following I/O power rails may rise in any sequence (see

Figure 34): QVDD, NVDD, GVDD1, and GVDD2.

Table 39. Power Supply Ramp Rate

Parameter

Min

Max

Unit

Required ramp rate.

—

36000

V/s

Notes:

1.

Ramp time is specified as a linear ramp from 10% to 90% of nominal voltage of the specific voltage supply. If the ramp is

non-linear (for example, exponential), the maximum rate of change from 200 to 500 mV is the most critical because this range

might falsely trigger the ESD circuitry.

2.

Required over the full recommended operating temperature range (see Table 3).

3.

All supplies must be at their stable values within 50 ms.

Figure 34. Supply Ramp-Up Sequence

VDD, MVDD, M3VDD

90%

NVDD, QVDD, GVDD1, GVDD2

相關PDF資料 |

PDF描述 |

|---|---|

| MSM5547RS | 0 TIMER(S), REAL TIME CLOCK, PDIP42 |

| MSM58321RS | 0 TIMER(S), REAL TIME CLOCK, PDIP16 |

| MSM6052GS | 4-BIT, MROM, MICROCONTROLLER, PQFP44 |

| MSM6242BGS | 1 TIMER(S), REAL TIME CLOCK, PDSO24 |

| MSM6255GS-BK | 128 X 256 CHARACTERS DOT MAT LCD DSPL CTLR, PQFP80 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8256SVT800B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSPStarcore 6-core RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| MSC8256TAG1000B | 制造商:Freescale Semiconductor 功能描述:STARCORE DSP, 6X 1GHZ SC3850 CORES, DDR2/3, SRIO, PCIE, QE, - Trays 制造商:Freescale Semiconductor 功能描述:IC DSP 6X 1GHZ SC3850 783FCBGA |

| MSC8256TVT1000B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSPStarcore 6-core RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| MSC8256TVT800B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSPStarcore 6-core RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| MSC83301 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS GENERAL PURPOSE AMPLIFIER APPLICATIONS |

發(fā)布緊急采購,3分鐘左右您將得到回復。