- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT8980 (Mitel Networks Corporation) () PDF資料下載

參數(shù)資料

| 型號: | MT8980 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | () |

| 中文描述: | () |

| 文件頁數(shù): | 7/11頁 |

| 文件大小: | 80K |

| 代理商: | MT8980 |

Application Note

MSAN-123

A-111

4.1 Switching Mode

A delay through the MT8980 results when

transferring channel information from an ST-BUS

input stream to an output stream. The input

information must first be transferred to the Data

Memory, where it waits until the next available

timeslot allocated to the output channel. Recalling

the definition of the ST-BUS, 32 channels arrive at an

input and 32 channels leave an output. Each

channel is allocated one timeslot per frame, so there

are 31 timeslots intervening between each timeslot

allocated to a particular channel. If the information

has just missed an appropriate timeslot for the

output channel, it may have to wait a number of

timeslots for the next allocated channel time.

The last bit of a channel is received before the

channel information is said to have entered the

MT8980 and is sent to the Data Memory.

Consequently, a channel’s information is sent to Data

Memory during the timeslot immediately following a

timeslot allocated to the channel. Conversely,

channel information is queued for an output channel

during the timeslot immediately preceding a timeslot

allocated to the channel.

The implication of this ordering of events is that

information entering the MT8980 cannot leave it in

the same timeslot, or in the timeslot immediately

following. Therefore, information that is to be output

in the same channel position as the information is

input, relative to frame pulse, will be output in the

following frame. As well, information switched to the

channel immediately following the input channel will

not be output in the timeslot immediately following

but in the next timeslot allocated to the output

channel, one frame later. Examples of channels

being switched to the channels immediately following

are: switching from Channel 1 to Channel 2, Channel

4 to Channel 5, Channel 30 to Channel 31, Channel

31 to Channel 0 etc. All of the channel changes

mentioned above are independent of stream

changes.

Whether the information can be output during the

second timeslot after the information entered the

MT8980 depends on which ST-BUS stream the

channel information enters on and which ST-BUS

stream the information leaves on. This situation is

caused by the order in which input stream

information is placed into Data Memory and the

order in which stream information is queued for

output.

Table

1

shows

streamcombinations that would allow information to

leave on the second timeslot after the information

was received.

the

input/output

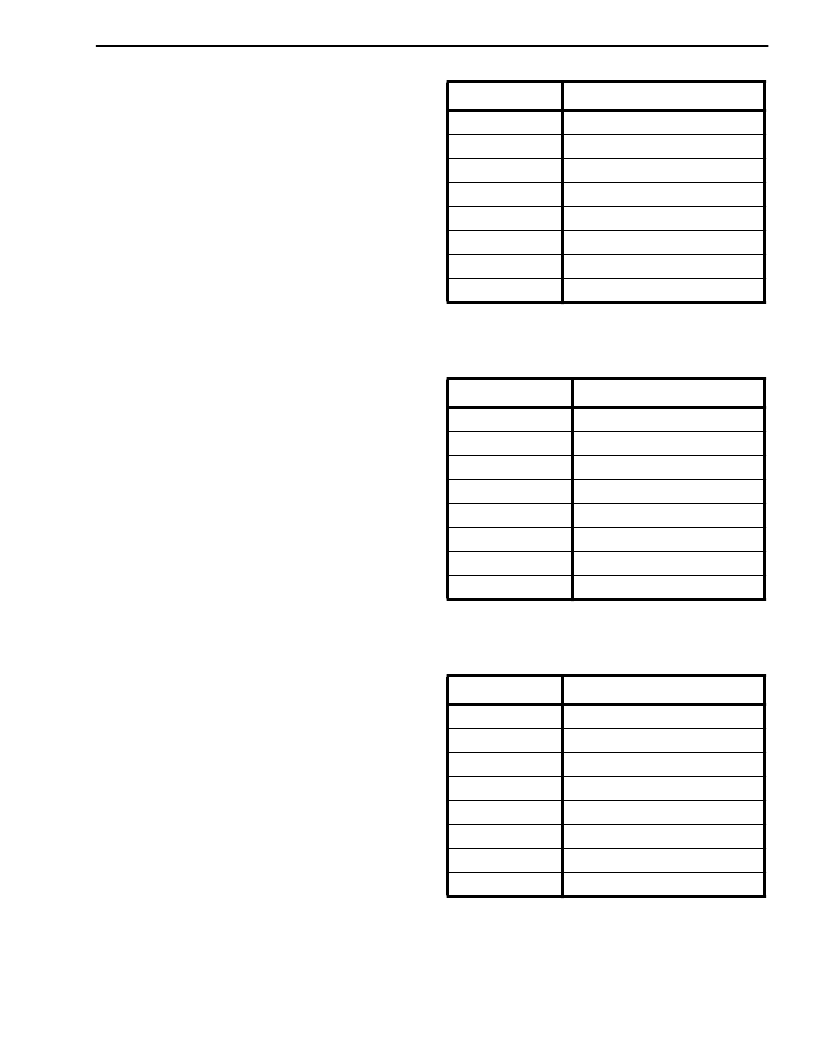

Table 1. Input Stream to Output Stream

Combinations that can Provide the

Minimum 2 Channel Delay

Table 2. Minimum Setup Times for Writing

to a Channel in Message Mode (Relative to

the Start of the Channel)

.

Table 3. Minimum Delays for Reading Input

Channels from Microprocessor Port. Delay

is Relative to End of Channel

Information can always leave the MT8980 by the

third

timeslot

after

entering

independent of which stream it is input on and which

the

MT8980,

Input Stream

Output Stream

0

1,2,3,4,5,6,7

1

3,4,5,6,7

2

5,6,7

3

7

4

1,2,3,4,5,6,7

5

3,4,5,6,7

6

5,6,7

7

7

Output Stream

Minimum Setup time

0

t

CLK

×

19

t

CLK

×

19

t

CLK

×

15

t

CLK

×

15

t

CLK

×

11

t

CLK

×

11

t

CLK

×

7

t

CLK

×

7

1

2

3

4

5

6

7

Input Stream

Minimum Delays

0

t

CLK

×

1

t

CLK

×

5

t

CLK

×

9

t

CLK

×

13

t

CLK

×

1

t

CLK

×

5

t

CLK

×

9

t

CLK

×

13

1

2

3

4

5

6

7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8982 | ISO-CMOS ST-BUS⑩ FAMILY Small Digital Switch (MiniDX) |

| MT8982AC | ISO-CMOS ST-BUS⑩ FAMILY Small Digital Switch (MiniDX) |

| MT8982AE | ISO-CMOS ST-BUS⑩ FAMILY Small Digital Switch (MiniDX) |

| MT8982AN | ISO-CMOS ST-BUS⑩ FAMILY Small Digital Switch (MiniDX) |

| MT8982AS | ISO-CMOS ST-BUS⑩ FAMILY Small Digital Switch (MiniDX) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8980D | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:ISO-CMOS ST-BUS Family Digital Switch |

| MT8980D-1 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY Digital Switch |

| MT8980DE | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 256 X 256 5V 40PDIP - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:SWIT FABRIC 256 X 256 5V 40PDIP - Rail/Tube |

| MT8980DE1 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 256 X 256 5V 40PDIP - Rail/Tube 制造商:Microsemi Corporation 功能描述:PB FREE DIGITAL SWITCH 制造商:Zarlink Semiconductor Inc 功能描述:SWIT FABRIC 256 X 256 5V 40PDIP - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE DIGITAL SWITCH |

| MT8980DP | 制造商:Mitel Networks Corporation 功能描述: 制造商:ZARLINK 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。