- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT89L86AP (Mitel Networks Corporation) CMOS ST-BUS⑩ FAMILY Multiple Rate Digital Switch PDF資料下載

參數(shù)資料

| 型號: | MT89L86AP |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | CMOS ST-BUS⑩ FAMILY Multiple Rate Digital Switch |

| 中文描述: | 意法半導(dǎo)體的CMOS總線⑩家庭多速率數(shù)字開關(guān) |

| 文件頁數(shù): | 10/40頁 |

| 文件大小: | 173K |

| 代理商: | MT89L86AP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

MT89L86

Advance Information

10

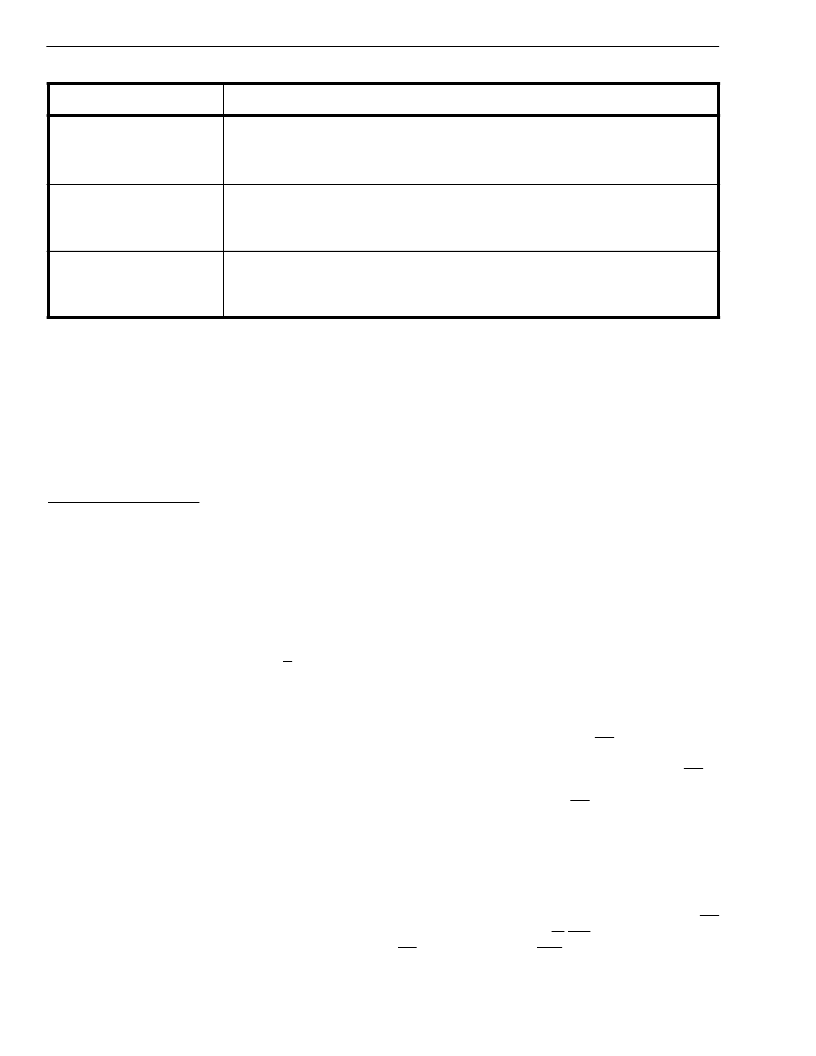

Table 4 - Constant Throughput Delay values

Data Rate

Throughput Delay (d)

2.048 Mb/s

d=[32 + (32 - IN) + (OUT - 1)]; (expressed in # time-slots)

2.048 Mb/s time-slot: 3.9

μ

s

IN: input time-slot (from 1 to 32)

OUT: output time-slot (from 1 to 32)

4.096 Mb/s

d=[64 + (64 - IN) + (OUT - 1)]; (expressed in # time-slots)

4.096 Mb/s time-slot: 1.95

μ

s

IN: input time-slot (from 1 to 64)

OUT: output time-slot (from 1 to 64)

8.192 Mb/s

d=[128 + (128 - IN) + (OUT - 1)]; (expressed in # time-slots)

8.192 Mb/s time-slot: 0.975

μ

s

IN: input time-slot (from 1 to 128)

OUT: output time-slot (from 1 to 128)

configurations with input and output channels that

provides more than its corresponding minimum

throughput delay, will have a throughput delay equal

to the difference between the output and input

channels; i.e., the throughput delay will be less than

one frame period. Table 3a shows the throughput

delay for each data rate operation.

Different I/O Data Rates

Except for the 2 Mb/s to 4 Mb/s and the 2 Mb/s to 8

Mb/s rate conversion operations, the throughput

delay from the MT89L86 may vary according to the

output stream used for switching.

Table 3b explains the worst case conditions for the

throughput delay when different I/O data rate

switching configurations are used.

Constant Throughput Delay mode (V/C bit = 1)

In this mode frame sequence integrity is maintained

in both Identical and Different I/O Data Rate

operations by making use of a multiple Data-Memory

buffer technique. The input channels written in any of

the buffers during frame N will be read out during

frame N+2. In applications at 2.048 Mb/s for

instance, the minimum throughput delay achievable

in constant delay mode will be 32 time-slots; for

example, when input time-slot 32 (channel 31) is

switched to output time-slot 1 (channel 0). Likewise,

the maximum delay is achieved when the first time

slot in a frame (channel 0) is switched to the last

time-slot in the frame (channel 31), resulting in 94

time-slots of delay.

To summarize, any input time-slot from input frame N

will always be switched to the destination time-slot

on output frame N+2. Table 4 describes the constant

throughput delay values at different data rates.

Microprocessor Port

The non-multiplexed bus interface provided by the

MT89L86 is identical to that provided in the MT8986

Digital Switch device. In addition to the non-

multiplexed bus, this 3.3V MT89L86 device provides

an

enhanced

microprocessor

multiplexed bus structure compatible to both

Motorola and Intel buses. The multiplexed bus

structure is selected by the CPU Interface Mode (IM)

input pin.

interface

with

If the IM input pin is connected to ground, the

MT89L86’s parallel port assumes its default Motorola

non-multiplexed bus mode identical to that of

MT8986. If the IM input is connected HIGH, the

internal parallel microprocessor port provides

compatibility to MOTEL (

MO

torola and In

TEL

compatible bus) interface allowing direct connection

to Intel, National and Motorola CPUs.

The on-chip MOTEL circuit automatically identifies

the type of CPU Bus connected to the device. This

circuit uses the level of the DS/RD input pin at the

rising edge of the AS/ALE to identify the appropriate

bus timing connected to the MT89L86. If DS/RD is

LOW at the rising edge of AS/ALE then the Motorola

bus timing is selected. If DS/RD is HIGH at the rising

edge of AS/ALE, the Intel bus timing is selected.

When the parallel port of this device is operating in

Motorola,

National

or

interfaces, the signals available for controlling the

device are: AD0-AD7 (Data and Address), ALE/AS

(Address Latch Enable/Address Strobe), DS/RD

(Data Strobe/Read), R/W\WR (Read/Write\Write),

CS (Chip Select) and DTA (Data Acknowledgment).

In the Motorola non-multiplexed bus mode, the

interface control signals are: data bus (AD0-AD7),

Intel

multiplexed

bus

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90210 | Multi-Rate Parallel Access Circuit(并行多路存取電路) |

| MT90210 | Multi-Rate Parallel Access Circuit |

| MT90210AL | Multi-Rate Parallel Access Circuit |

| MT90220 | Octal IMA/UNI PHY Device(八端口 IMA/UNI 物理層設(shè)備(八端口ATM IMA和UNI處理器)) |

| MT90221 | Quad IMA/UNI PHY Device(四端口 IMA/UNI 物理層設(shè)備(四端口ATM IMA和UNI處理器)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT89L86AP1 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 256 X 256/512 X 256/128 X 128 131.072MBPS 3.3V 4 - Rail/Tube 制造商:Microsemi Corporation 功能描述:IC TDM/TSI SWITCH 512X256 44PLCC |

| MT89L86APR1 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 256 X 256/512 X 256/128 X 128 131.072MBPS 3.3V 4 - Tape and Reel 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM/TSI SWITCH 512X256 44PLCC 制造商:Microsemi Corporation 功能描述:IC TDM/TSI SWITCH 512X256 44PLCC |

| MT8D132 | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:1 MEG, 2 MEG x 32 DRAM MODULES |

| MT8D132-10 | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:1 MEG, 2 MEG x 32 DRAM MODULES |

| MT8D132-6 | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:1 MEG, 2 MEG x 32 DRAM MODULES |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。