- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT90210 (Mitel Networks Corporation) Multi-Rate Parallel Access Circuit PDF資料下載

參數(shù)資料

| 型號(hào): | MT90210 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Multi-Rate Parallel Access Circuit |

| 中文描述: | 多速率電路并行訪問 |

| 文件頁(yè)數(shù): | 4/27頁(yè) |

| 文件大小: | 133K |

| 代理商: | MT90210 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

MT90210

Preliminary Information

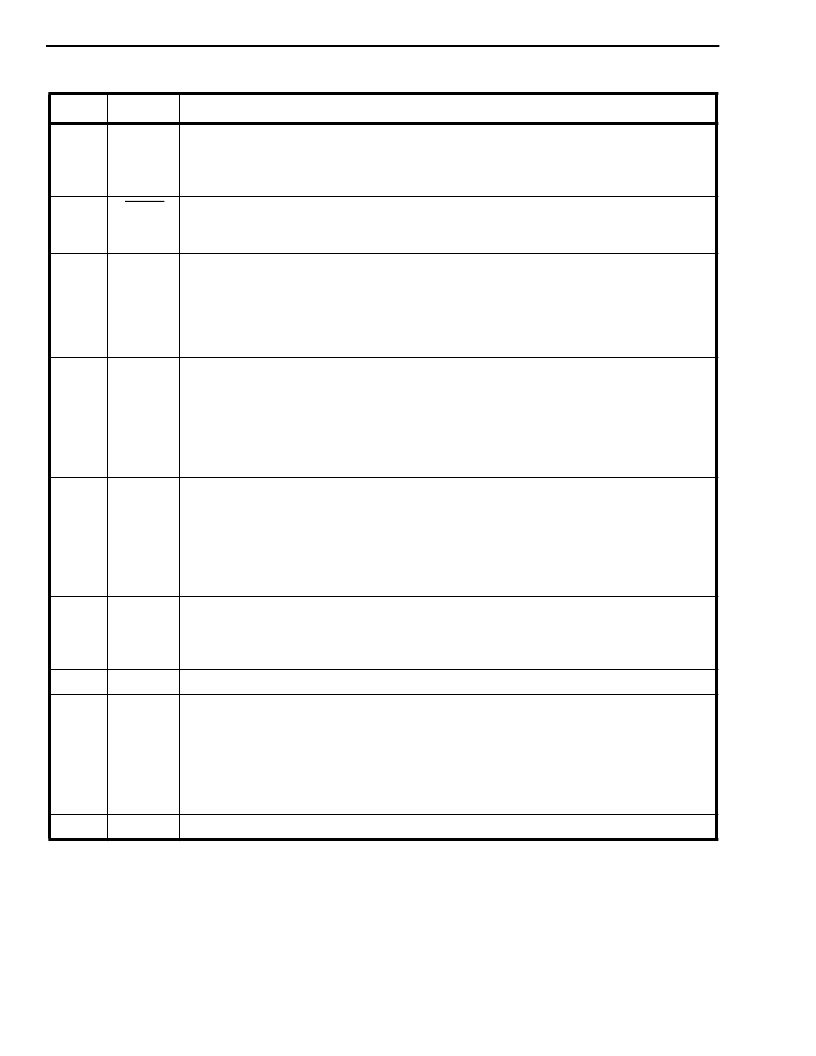

2-148

58-59,

61-62,

64,

66-68

P0-P1,

P2-P3,

P4,

P5-P7

Parallel Input/Output Data Bus.

This 8 bit data bus is a bidirectional parallel port used to

perform 8-bit transactions between the MT90210 and the external dual port RAM. Data is

clocked in and out of the P0-P7 parallel port according to Figures 22 and 23.

70

Strobe

Strobe Output.

This output is typically connected to the Chip-enable input of the external

dual port RAM. It is kept low during all read cycles, stays high during inactive periods and

goes low for the last half of a memory write cycle.

72-73,

75- 77,

80-82,

84-85,

87,

89-90

A0-A1,

A2-A4,

A5-A7,

A8-A9,

A10,

A11-A12

External Memory Address Outputs A0-A12.

These 13 address output lines are provided

by the MT90210 to allow a direct connection to an external dual port RAM.

91

RBC

Read Data Block Complete (output)

. A transition on this output is used to notify the

external CPU that the MT90210 has finished reading the contents of one entire 125

μ

s

frame from the external dual port memory (e.g.; from addresses 0000h to 0FFFh in modes

3, 4 or 5). Whenever RBC toggles, the MT90210 starts reading the next half of the memory

(addresses 1000h to 1FFFh) while the local CPU updates the first half with more data to

be sent. RBC toggles every 125

μ

s. When this signal is low, the MT90210 is reading the

lower memory block.

94

WBC

Write Data Block Complete (Output).

A transition on this output is used to notify the

external CPU that the MT90210 has finished writing the contents of one entire 125

μ

s

frame into the external dual port memory (e.g; from addresses 0000h to 0FFFh in modes

3,4 or 5). Once WBC toggles, the local CPU can access the Dual port memory to get the

data while the MT90210 writes the contents of the next 125

μ

s frame into the other half

(addresses 1000h to 1FFFh) of the dual port memory. WBC toggles every 125

μ

s. When

this signal is low, the MT90210 is writing to the lower memory block.

4,16,

63, 71,

78, 86,

92, 99

V

DD

Supply Input.

+5V.

41, 55

V

DD2

Supply Input.

+5V.

5,10,

17, 23,

60, 65,

69, 74,

79,83,

88, 93,

98

V

SS

Ground.

28

V

SS2

Ground.

Pin Description (continued)

Pin

Name

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90210AL | Multi-Rate Parallel Access Circuit |

| MT90220 | Octal IMA/UNI PHY Device(八端口 IMA/UNI 物理層設(shè)備(八端口ATM IMA和UNI處理器)) |

| MT90221 | Quad IMA/UNI PHY Device(四端口 IMA/UNI 物理層設(shè)備(四端口ATM IMA和UNI處理器)) |

| MT90401 | SONET/SDH System Synchronizer(SONET/SDH 系統(tǒng)同步裝置(由一個(gè)數(shù)字鎖相環(huán)組成)) |

| MT9040 | T1/E1 Synchronizer(T1/E1 系統(tǒng)同步裝置(由一個(gè)數(shù)字鎖相環(huán)組成)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90210AL | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Multi-Rate Parallel Access Circuit |

| MT90220 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Octal IMA/UNI PHY Device |

| MT90220AL | 制造商:Zarlink Semiconductor Inc 功能描述:I.C. |

| MT90220ALX01 | 制造商:Mitel Networks Corporation 功能描述: |

| MT90221 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Quad IMA/UNI PHY Device |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。