- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359243 > MVTX2801AG (ZARLINK SEMICONDUCTOR INC) Unmanaged 4-Port 1000 Mbps Ethernet Switch PDF資料下載

參數(shù)資料

| 型號: | MVTX2801AG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | Unmanaged 4-Port 1000 Mbps Ethernet Switch |

| 中文描述: | DATACOM, LAN SWITCHING CIRCUIT, PBGA596 |

| 封裝: | 40 X 40 MM, 2.33 MM HEIGHT, MS-034, HSBGA-596 |

| 文件頁數(shù): | 14/106頁 |

| 文件大小: | 1455K |

| 代理商: | MVTX2801AG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

MVTX2801

Data Sheet

14

Zarlink Semiconductor Inc.

As at the transmit end, each of the 4 ports has time slots devoted solely to reading data from memory at the address

calculated by port control. The Transmission DMA (TxDMA) is responsible for multiplexing the data and the address.

On a port's turn, the TxDMA will move 8 bytes (or up to the EOF) from memory into the port's associated TxFIFO.

After reading the EOF, the port control requests a FCB release for that frame. The TxDMA arbitrates among multiple

buffer release requests.

The frame is transmitted from the TxFIFO to the line.

3.2 Multicast Data Frame Forwarding

After receiving the switch response, the TxQ manager has to make the dropping decision. A global decision to drop

can be made, based on global FDB utilization and reservations. If so, then the FCB is released and the frame is

dropped. In addition, a selective decision to drop can be made, based on the TxQ occupancy at some subset of the

multicast packet's destinations. If so, then the frame is dropped at some destinations but not others, and the FCB is

not released. If the frame is not dropped at a particular destination port, then the TxQ manager formats an entry in

the multicast queue for that port and class. Multicast queues are physical queues (unlike the linked lists for unicast

frames). There are 4 multicast queues for each of the 4 Gigabit ports.

During scheduling, the TxQ manager treats the unicast queue and the multicast queue of the same class as one

logical queue.

The port control requests a FCB release only after the EOF for the multicast frame has been read by all ports to

which the frame is destined.

4.0 Memory Interface

4.1 Overview

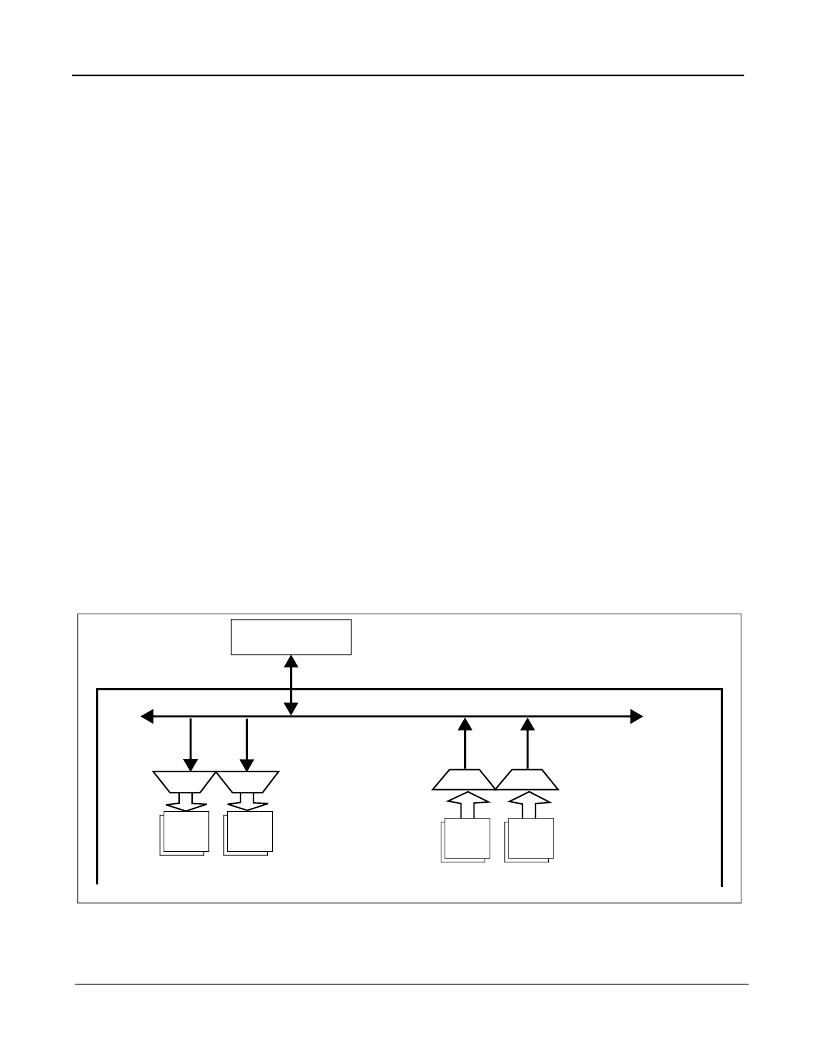

The figure below illustrates the first part of the ZBT-SRAM interface for the MVTX2801. As shown, a 64 bit bus

ZBT-SRAM bank A is used for Tx/RxDMA access. Because the clock frequency is 133 MHz, the total memory

bandwidth is 64-bits x 133 MHz = 8.5 Gbps, for frame data buffer (FDB) access.

Figure 3 - SRAM Interface Block Diagram (DMAs for Gigabit Ports)

TX DMA

2-3

TX DMA

0-1

RX DMA

2-3

RX DMA

0-1

ZBT-SRAM Bank A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MVTX2802 | Managed 4-Port 1000 Mbps Ethernet Switch |

| MVTX2802AG | Managed 4-Port 1000 Mbps Ethernet Switch |

| MVTX2803 | Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803AG | Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2804 | 8-Port 1000 Mbps Ethernet Distributed Switch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MVTX2802 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Managed 4-Port 1000 Mbps Ethernet Switch |

| MVTX2802A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Managed 4 port Gigabit Ethernet switch |

| MVTX2802AG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Managed 4-Port 1000 Mbps Ethernet Switch |

| MVTX2803 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Unmanaged 8 port Gigabit Ethernet switch |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。