- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369939 > P28F002BC-T120 (INTEL CORP) 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY PDF資料下載

參數(shù)資料

| 型號(hào): | P28F002BC-T120 |

| 廠商: | INTEL CORP |

| 元件分類: | PROM |

| 英文描述: | 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| 中文描述: | 256K X 8 FLASH 12V PROM, 120 ns, PDIP40 |

| 封裝: | PLASTIC, DIP-40 |

| 文件頁(yè)數(shù): | 14/37頁(yè) |

| 文件大小: | 455K |

| 代理商: | P28F002BC-T120 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

28F002BC 2-MBIT BOOT BLOCK FLASH MEMORY

E

14

PRELIMINARY

3.2.2

INTELLIGENT IDENTIFIERS

The manufacturer and device codes are read via

the CUI or by taking the A

9

pin to V

ID

. Writing 90H

to the CUI places the device into Intelligent

Identifier read mode. A read of location 00000H

outputs the manufacturer’s identification code, 89H.

Reading location 00001H outputs the device ID,

7CH.

The 28F002BC device ID of 7CH is identical to the

E28F002BX (40-lead TSOP). It differs from the

PA28F200BX (44-lead PSOP), which has a device

ID of 2274H. Designers using the PA28F200BX in

the x8 mode who wish to migrate to the

PA28F002BC need to be mindful of this device ID

difference

and

modify

necessary. The 40-lead PDIP device ID is 7CH.

software

drivers

as

3.3

Write Operations

There are two commands that alter memory array

contents: Program Setup and Erase Setup/Confirm.

In addition, the Erase Suspend command suspends

the WSM during an erase operation and releases

the CUI to accept any Read command (so long as it

is to a block other than the one being erased).

Finally, there is a Clear Status Register command

for resetting the contents of the status register. This

command

should

be

operations that modify the status register.

invoked

following

all

All commands written to the CUI will be interpreted,

but for any write operation to be initiated, the V

PP

voltage must be at V

HH

. Depending on the

application, the design may have a switchable V

PP

power supply or the V

PP

may be “hard-wired” to

12V. The 28F002BC will function normally in either

case. It is highly recommended that RP# is tied to

the system RESET for data protection during

unstable CPU reset and also for proper CPU / flash

synchronization.

Furthermore, when attempting to modify the

contents of the 28F002BC’s boot block area, V

HH

must be applied to both V

PP

and RP# for the

operation to be valid. Whether attempting to alter

the contents of the boot block or any other memory

array area, if the proper voltages are not applied to

the correct input signals the write operation will be

aborted. Subsequently, the status register will

respond with either Bit 3 (V

PP

low error), Bit 4

(program error) or Bit 5 (erase error) being set (refer

to Table 5 for status register definitions).

3.3.1

COMMAND USER INTERFACE (CUI)

The Command User Interface (CUI) serves as the

interface between the microprocessor and the

internal chip controller. Commands are written to

the CUI using standard microprocessor write

timings. The available commands (summarized in

Tables 3 and 4) are Read Array, Read Intelligent

Identifier, Read Status Register, Clear Status

Register, Program Setup, Erase Setup/Confirm,

and Erase Suspend.

For Read commands, the CUI points the read path

at either the array, the intelligent identifier, or the

status register depending on the command

received. For Program or Erase commands, the

CUI informs the Write State Machine (WSM) that a

Program or Erase has been requested. During the

execution of a Program command, the WSM

controls the programming sequences and the CUI

responds only to status register reads. During an

erase cycle, the CUI responds only to status

register reads and Erase Suspend. After the WSM

has completed its task, it will set the WSM Status

bit (bit 7 of the status register) to a “1,” which will

also allow the CUI to respond to its full command

set. Note that after the WSM has returned control to

the CUI, the CUI will stay in the read status register

mode until it receives another command (see

Appendix B).

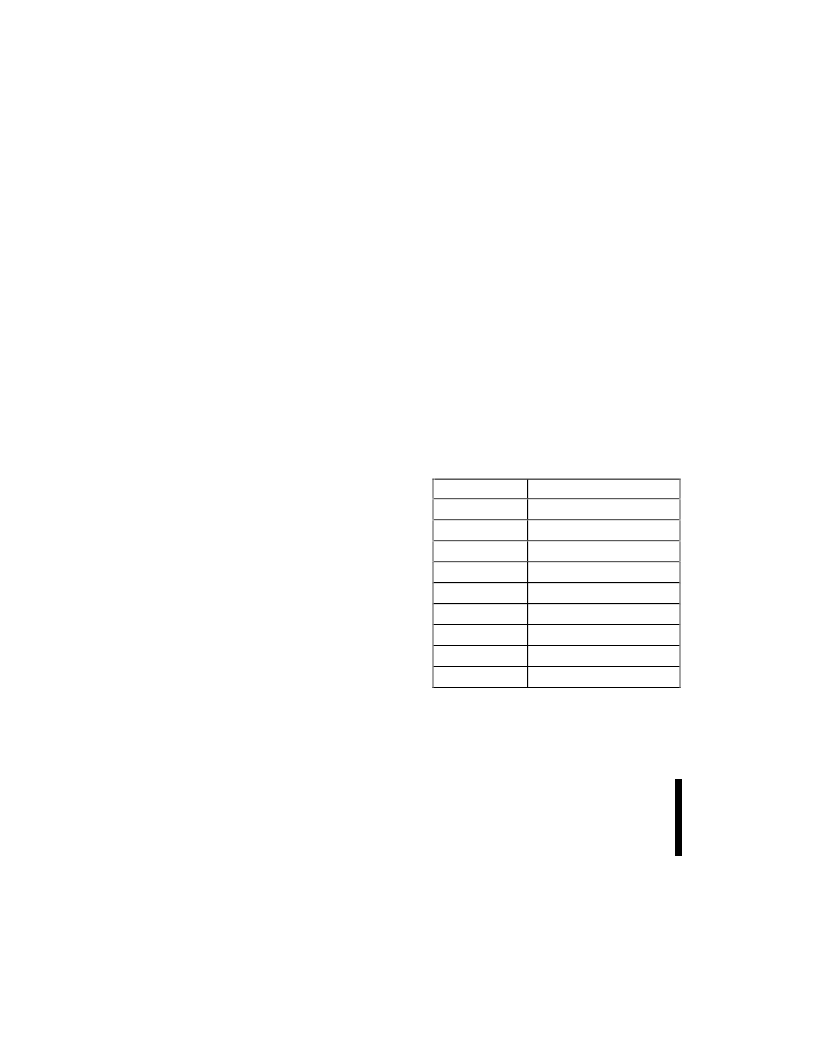

Table 3. Command Set Codes and

Corresponding Device Mode

Command Codes

Device Mode

00

Invalid/Reserved

20

Erase Setup

40

Program Setup

50

Clear Status Register

70

Read Status Register

90

Intelligent Identifier

B0

Erase Suspend

D0

Erase Resume/Erase Confirm

FF

Read Array

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P28F002BC-T80 | 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| P28F512-150 | 512K(64Kx8)CMOS FLASH MEMORY |

| P28F512-120 | 512K(64Kx8)CMOS FLASH MEMORY |

| P3000AA61 | solid state crowbar devices |

| P3104U | solid state crowbar devices |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P28F002BC-T80 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| P28F010120 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| P28F010-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F010 1024K (128K X 8) CMOS FLASH MEMORY |

| P28F010150 | 制造商:INTEL 功能描述:* |

| P28F010-150 | 制造商:Intel 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。