- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367724 > P80CL51 (NXP Semiconductors N.V.) Low voltage 8-bit microcontrollers with UART PDF資料下載

參數(shù)資料

| 型號(hào): | P80CL51 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Low voltage 8-bit microcontrollers with UART |

| 中文描述: | 低電壓的8位微控制器的UART的 |

| 文件頁數(shù): | 31/68頁 |

| 文件大小: | 305K |

| 代理商: | P80CL51 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

1997 Apr 15

31

Philips Semiconductors

Product specification

Low voltage 8-bit microcontrollers with

UART

P80CL31; P80CL51

14 INTERRUPT SYSTEM

External events and the real-time-driven on-chip

peripherals require service by the CPU at unpredictable

times. To tie the asynchronous activities of these functions

to normal program execution a multiple-source,

two-priority-level, nested interrupt system is provided.

The system is shown in Fig.19. The P80CLx1

acknowledges interrupt requests from thirteen sources as

follows:

INT0 to INT9

Timer 0 and Timer 1

UART.

Each interrupt vectors to a separate location in Program

Memory for its service routine. Each source can be

individually enabled or disabled by corresponding bits in

the Interrupt Enable Registers (IEN0 and IEN1).

The priority level is selected via the Interrupt Priority

Registers (IP0 and IP1). All enabled sources can be

globally disabled or enabled. Figure 19 shows the interrupt

system.

14.1

External interrupts INT2 to INT9

Port 1 lines serve an alternative purpose as eight

additional interrupts INT2 to INT9. When enabled, each of

these lines may wake-up the device from the Power-down

mode. Using the Interrupt Polarity Register (IX1), each pin

may be initialized to be either active HIGH or active LOW.

IRQ1 is the Interrupt Request Flag Register. If the interrupt

is enabled, each flag will be set on an interrupt request but

must be cleared by software, i.e. via the interrupt software

or when the interrupt is disabled.

Port 1 interrupts are level sensitive. A Port 1 interrupt will

be recognized when a level (HIGH or LOW depending on

the Interrupt Polarity Register) on P1.n is held active for at

least one machine cycle. The interrupt request is not

serviced until the next machine cycle. Figure 20 shows the

external interrupt configuration.

14.2

Interrupt priority

Each interrupt source can be set to either a high priority or

to a low priority. If a low priority interrupt is received

simultaneously with a high priority interrupt, the high

priority interrupt will be dealt with first.

If interrupts of the same priority are requested

simultaneously, the processor will branch to the interrupt

polled first, according to the sequence shown in Table 9

and in Fig.19. The ‘vector address’ is the ROM location

where the appropriate interrupt service routine starts.

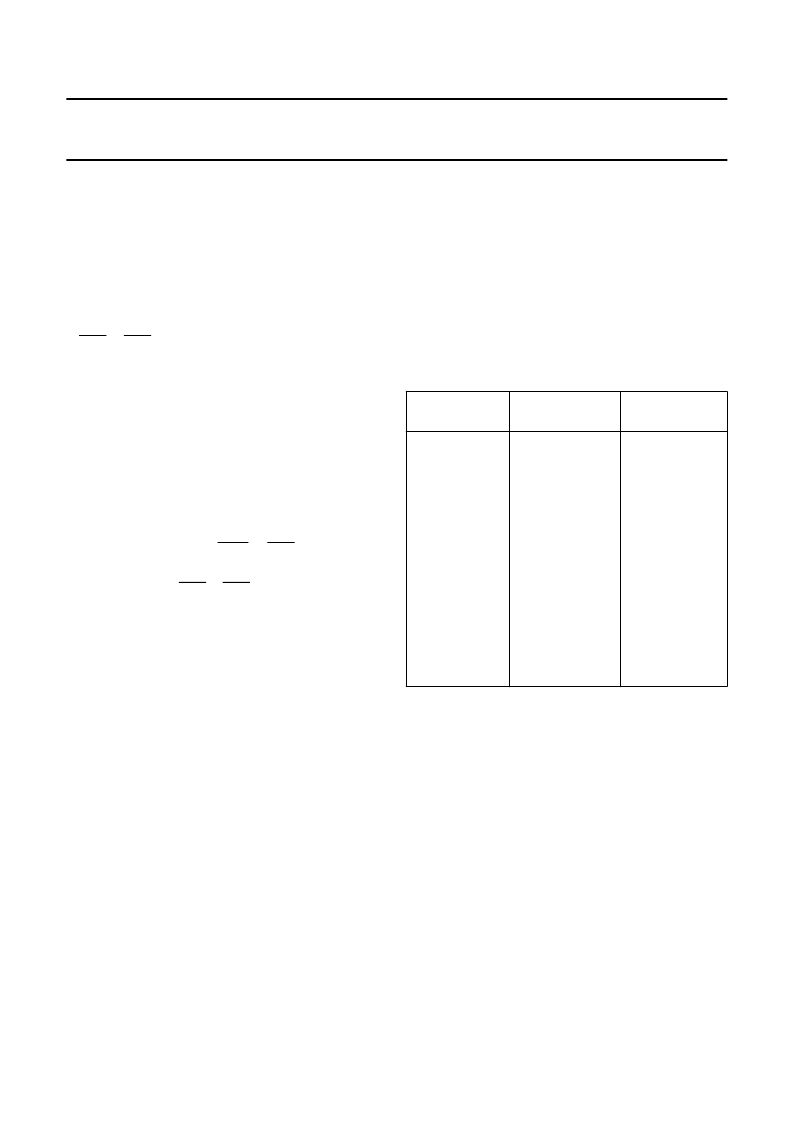

Table 9

Interrupt vector polling sequence

A low priority interrupt routine can only be interrupted by a

high priority interrupt. A high priority interrupt routine

cannot be interrupted.

SYMBOL

VECTOR

ADDRESS (HEX)

SOURCE

X0 (first)

S0

X5

T0

X6

X1

X2

X7

T1

X3

X8

X4

X9 (last)

0003

002B

0053

000B

005B

0013

003B

0063

001B

0043

006B

004B

0073

External 0

UART

External 5

Timer 0

External 6

External 1

External 2

External 7

Timer 1

External 3

External 8

External 4

External 9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P80CL51HFT | Low voltage 8-bit microcontrollers with UART |

| P80CL410HFP | Low voltage 8-bit microcontrollers with I2C-bus |

| P83CL410HFH | Low voltage 8-bit microcontrollers with I2C-bus |

| P83CL410HFP | Low voltage 8-bit microcontrollers with I2C-bus |

| P80CL410HFT | Low voltage 8-bit microcontrollers with I2C-bus |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P80CL51HFH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low-voltage single-chip 8-bit microcontrollers |

| P80CL51HFHB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low-voltage single-chip 8-bit microcontrollers |

| P80CL51HFP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low voltage 8-bit microcontrollers with UART |

| P80CL51HFPN | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low-voltage single-chip 8-bit microcontrollers |

| P80CL51HFT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low-voltage single-chip 8-bit microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。