- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367799 > PC755BVZFU400LD MICROPROCESSOR|32-BIT|CMOS|BGA|360PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號(hào): | PC755BVZFU400LD |

| 英文描述: | MICROPROCESSOR|32-BIT|CMOS|BGA|360PIN|PLASTIC |

| 中文描述: | 微處理器| 32位|的CMOS | BGA封裝| 360PIN |塑料 |

| 文件頁(yè)數(shù): | 31/48頁(yè) |

| 文件大小: | 276K |

| 代理商: | PC755BVZFU400LD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

PC755B/745B

31/48

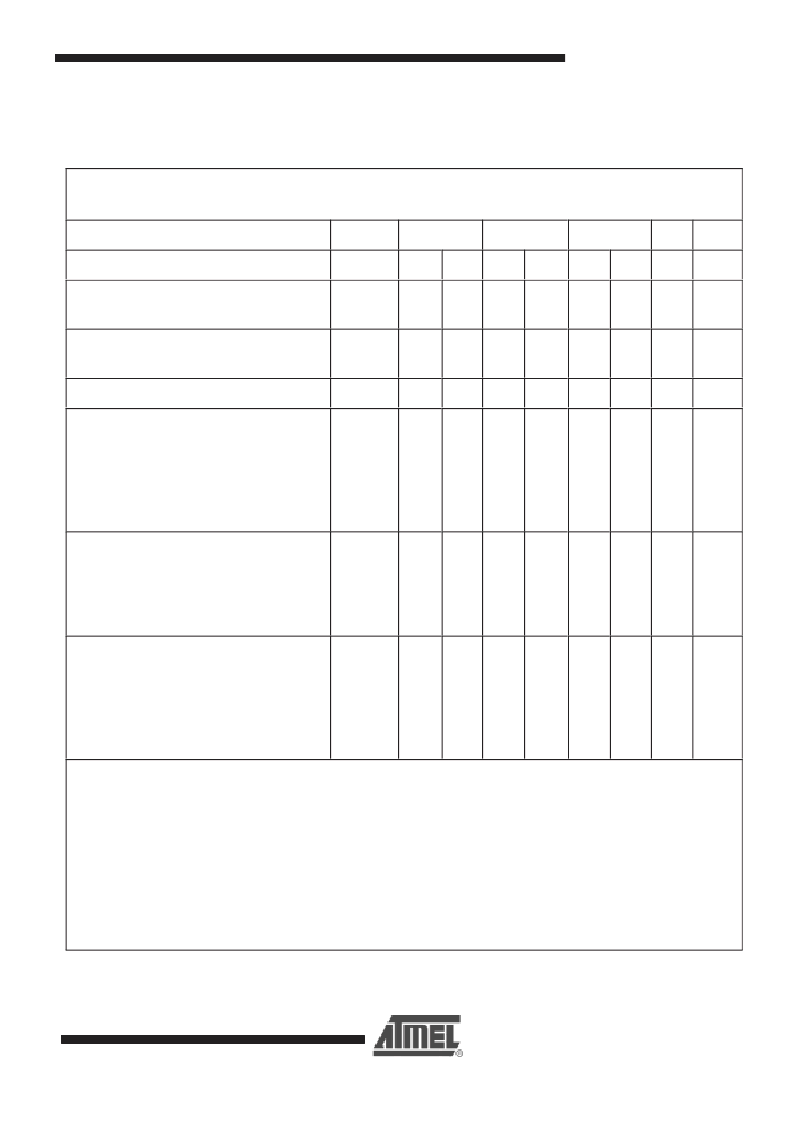

4.2.4. L2 Bus Input AC Specifications

Table 14 provides the L2 bus interface AC timing specifications for the PC755B as defined in Figure 15 and Figure 16 for the loading

conditions described in Figure 17.

Table 14. L2 Bus Interface AC Timing Specifications

At Vdd=AVdd=2.0V 100mV; -55

Tj

+125

o

C, OVdd = 3.3V 165mV and OVdd = 1.8V 100mV and OVdd = 2.0V 100mV

Parameter

Symbol

300 MHz

350 MHz

400 MHz

Unit

Notes

Min

Max

Min

Max

Min

Max

L2SYNC_IN rise and fall time

tL2CR&

tL2CF

—

1.0

—

1.0

—

1.0

ns

1

Setup Times: Data and parity

tDVL2CH

1.5

—

1.5

—

1.4

—

ns

2

Input Hold Times: Data and parity

tDXL2CH

0.5

—

0.5

—

0.5

—

ns

2

Valid Times:

All outputs when L2CR[14-15] = 00

All outputs when L2CR[14-15] = 01

All outputs when L2CR[14-15] = 10

All outputs when L2CR[14-15] = 11

tL2CHOV

–

–

–

3.6

3.8

4.0

4.2

–

–

–

–

3.6

3.8

4.0

4.2

–

–

–

–

3.6

3.8

4.0

4.2

ns

3,4

Output Hold Times

All outputs when L2CR[14-15] = 00

All outputs when L2CR[14-15] = 01

All outputs when L2CR[14-15] = 10

All outputs when L2CR[14-15] = 11

tL2CHOX

0.5

0.7

0.9

1.1

–

–

–

–

0.5

0.7

0.9

1.1

–

–

–

–

0.5

0.7

0.9

1.1

–

–

–

–

ns

3

L2SYNC_IN to high impedance:

All outputs when L2CR[14-15] = 00

All outputs when L2CR[14-15] = 01

All outputs when L2CR[14-15] = 10

All outputs when L2CR[14-15] = 11

tL2CHOZ

–

–

–

–

3.5

4.0

4.2

4.5

–

–

–

–

3.5

4.0

4.2

4.5

–

–

–

–

3.5

4.0

4.2

4.5

ns

3,5

Notes:

1. Rise and fall times for the L2SYNC_IN input are measured from 20% to 80% of L2OVdd.

2. All input specifications are measured from the midpoint of the signal in question to the midpoint voltage of the rising edge of

the input L2SYNC_IN (see

Figure 15). Input timings are measured at the pins.

3. All output specifications are measured from the midpoint voltage of the rising edge of L2SYNC_IN to the midpoint of the signal

in question. The output timings are measured at the pins. All output timings assume a purely resistive 50 ohm load (See

Figure 16 ).

4. he outputs are valid for both single-ended and differential L2CLK modes. For pipelined registered synchronous burst RAMs,

L2CR[14–15] = 01 or 10 is recommended. For pipelined late-write synchronous burst SRAMs, L2CR[14–15] = 11 is recom-

mended.

5. Guaranteed by design and characterization.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC745BMZFU350LD | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|PLASTIC |

| PC745BMZFU400LD | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|PLASTIC |

| PC745BVZFU300LD | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|PLASTIC |

| PC745BVZFU350LD | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|PLASTIC |

| PC745BVZFU400LD | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC755CMGHU300LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CMGHU350LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CMGHU366LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CMGHU400LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CMGSU300LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。