- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367813 > PCD6001H (NXP SEMICONDUCTORS) Digital telephone answering machine chip PDF資料下載

參數(shù)資料

| 型號: | PCD6001H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Digital telephone answering machine chip |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP80 |

| 封裝: | PLASTIC, QFP-80 |

| 文件頁數(shù): | 34/96頁 |

| 文件大小: | 385K |

| 代理商: | PCD6001H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

2001 Apr 17

34

Philips Semiconductors

Product specification

Digital telephone answering machine chip

PCD6001

10.7.2

P

ARALLEL FLASH INTERFACE

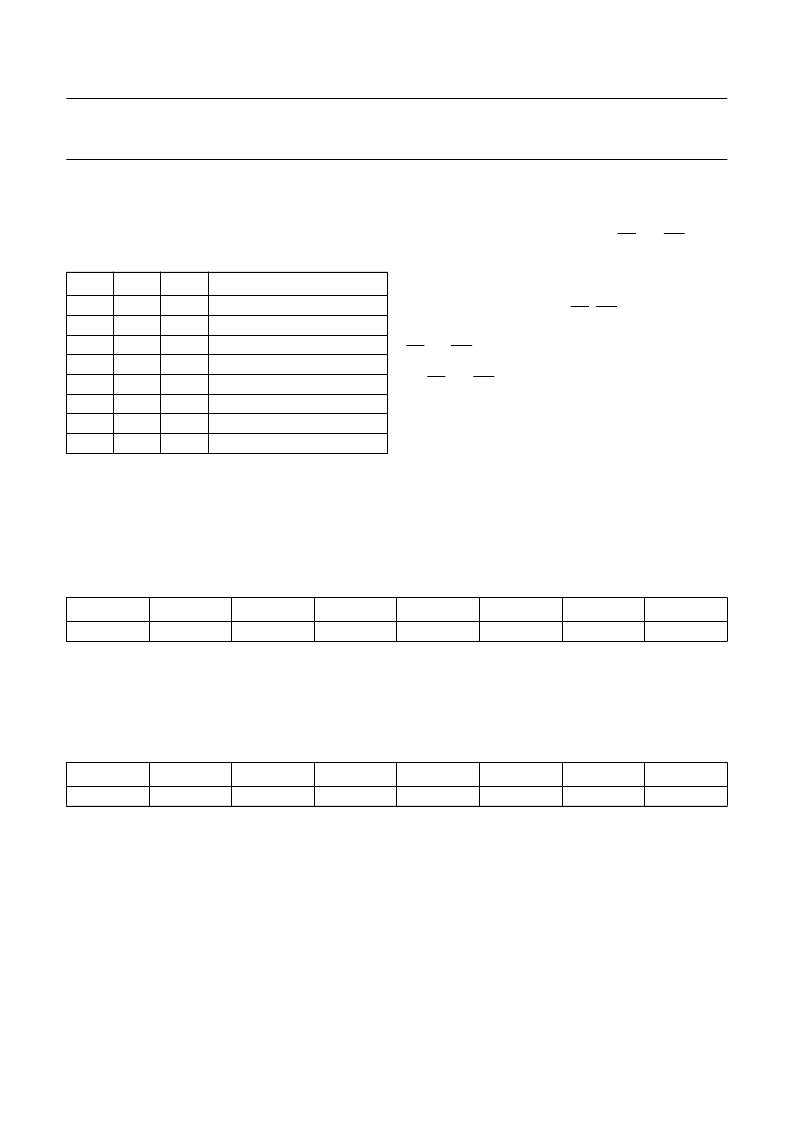

If a parallel (4-Mbit) flash memory is chosen Table 26 is

valid.

Table 26

Using P4 with 4-Mbit parallel flash memory

Since parallel flash memory has a much larger addressing

range than the 64 kbytes addressing capability of the

80CL51, additional addressing is done by means of the

P4 SFR and the P4 I/O pad. The P4 SFR is connected to

Port P4 as shown in Table 27.

One pin is necessary to enable and disable the flash

memory to reduce power consumption. Four pins of P4

are necessary to connect various types of flash memories:

A parallel flash: P4.0 to P4.2, P4.3, RD and WR are

connected to MA[16:18], CEN, OEN and WN

A serial flash: FSO, FSI, FSC and P4.3 are connected

to DI, DO, SK and CEN pins

A CAD flash: P4.1 to P4.3, RD, WR are connected to

CLE, ALE, CEN, REN and WEN pins.

RD and WR are available as separate pins. If an access is

done to the AUX RAM (ARD bit of PCON equals logic 0)

the RD and WR will be logic 1 on these pins.

Bits 1, 2and 4ofPort 4aresettoFSI,FSKandFSOwhen

a serial flash is selected in the MCSC SFR.

The P4 SFR is defined in Table 28. Bits P4.6 and P4.7 are

not available as addressable bits or port pins.

P4 pin behaviour and configuration is described in more

detail in Section 16.2.

P4.2

P4.1

P4.0

ADDRESS

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Bank 0: 00000H to 0FFFFH

Bank 1: 10000H to 1FFFFH

Bank 2: 20000H to 2FFFFH

Bank 3: 30000H to 3FFFFH

Bank 4: 40000H to 4FFFFH

Bank 5: 50000H to 5FFFFH

Bank 6: 60000H to 6FFFFH

Bank 7: 70000H to 7FFFFH

Table 27

P4 pin behaviour (alternative pin functions)

Note

1.

The alternative outputs (GPC, FSI, FSO, FSK and LE) are connected with the general purpose outputs via an AND

logic gate. Therefore when using the alternative functions the corresponding port bits have to be set to a logic 1.

10.7.2.1

Port 4 Register (P4)

Table 28

Port 4 Register (SFR address 98H); reset state 1EH

7

6

5

(1)

4

3

2

1

0

P4.5/GPC

P4.4/FSI

P4.3

P4.2/FSO

P4.1/FSK

P4.0/LE

7

6

5

4

3

2

1

0

P4.7

P4.6

P4.5

P4.4

P4.3

P4.2

P4.1

P4.0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD6001U | Digital telephone answering machine chip |

| PCD8582D-2P | 256 x 8-bit CMOS EEPROMS with I2C-bus interface |

| PCD8582D-2 | 256 x 8-bit CMOS EEPROMS with I2C-bus interface |

| PCD8582D-2T | 256 x 8-bit CMOS EEPROMS with I2C-bus interface |

| PCA8582F-2 | 256 x 8-bit CMOS EEPROMS with I2C-bus interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD6001U | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital telephone answering machine chip |

| PCD6002H/2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Solid-State Recorder |

| PCD6003 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital telephone answering machine chip |

| PCD6003H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital telephone answering machine chip |

| PCD6003U | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital telephone answering machine chip |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。