- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369949 > PCF8832 STN RGB - 384 output column driver PDF資料下載

參數(shù)資料

| 型號(hào): | PCF8832 |

| 英文描述: | STN RGB - 384 output column driver |

| 中文描述: | 超扭曲的RGB - 384列驅(qū)動(dòng)器輸出 |

| 文件頁(yè)數(shù): | 7/76頁(yè) |

| 文件大小: | 385K |

| 代理商: | PCF8832 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

2002 Aug 16

7

Philips Semiconductors

Preliminary specification

STN RGB - 384 output column driver

PCF8832

7

FUNCTIONAL DESCRIPTION

7.1

I/O buffer and interface

The interface is the connection between the outside world

and PCF8832. One of five industrial standard interfaces

can be selected using the interface configuration inputs

PS2, PS1 and PS0.

7.2

Configuration control

It is possible to configure the PCF8832s to use external

voltages, see Table 2.

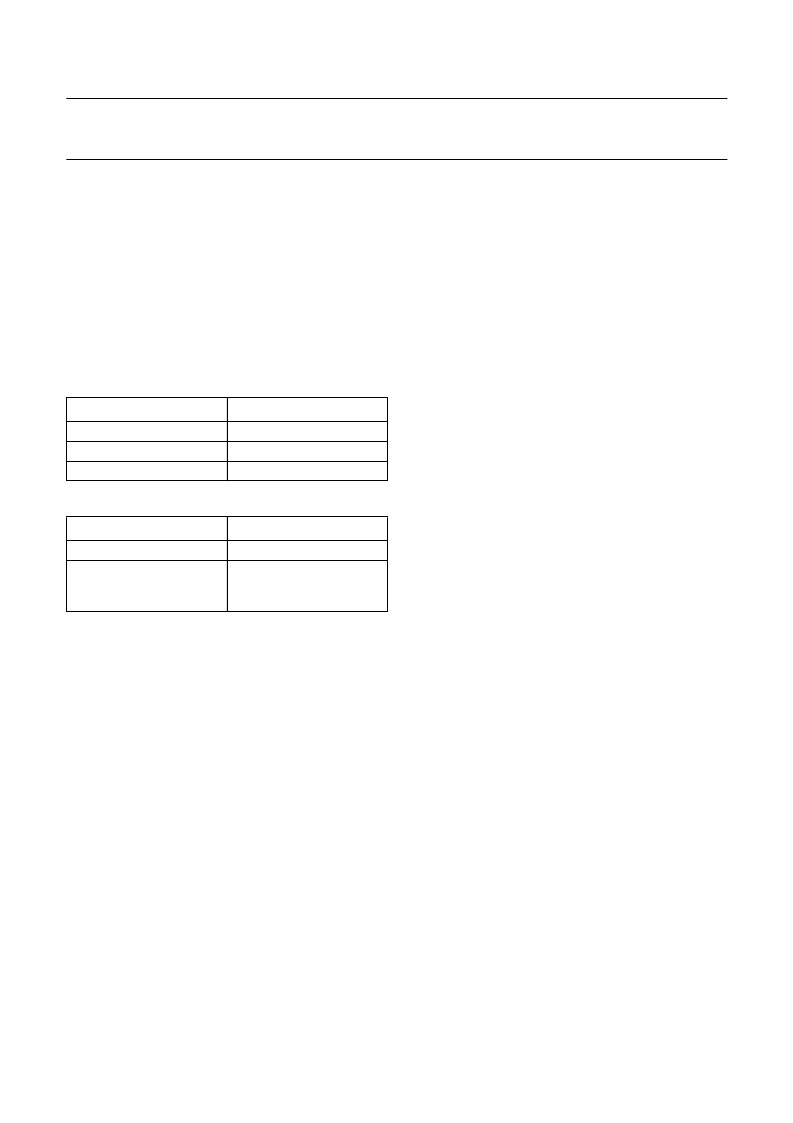

Table 1

Default configuration settings

Table 2

Analog circuit configuration

7.3

Oscillator

The on-chip oscillator provides the clock signal for the

display system. An external clock signal, if used, is

connected to the OSC input. In this case the internal

oscillator must be switched off by a software command.

To improve the timing accuracy there is an external

resistor option. If this option is used, the external resistor

must be connected between OSC and V

DD1

and the

appropriate register must be set. If the internal resistor is

selected, the OSC input must be left open-circuit.

7.4

Display data RAM

The Display Data RAM (DDRAM) is a 128

×

9

×

168-bit

static RAM for display data storage. During RAM access,

data is transferred to the DDRAM via the interface.

7.5

Address counter

The address counter sets the addresses of the display

data RAM for writing operations.

7.6

Display address counter

The display is generated by continuously reading-out rows

of RAM data to the dot matrix LCD via the column outputs.

The display status (all dots on/off and normal/inverse

video) is set via the interface.

7.7

Command decoder

The command decoder identifies command words arriving

at the interface and routes the following data bytes to their

destination.

7.8

DC-to-DC converter

The voltage multiplier generates the required column

voltage V

COL

. Pins CA1 and CA2 must be connected to an

external capacitor. If the capacitive DC-to-DC converter is

switched off by AOFF = 1, then V

COL

must be supplied

externally.

7.9

LCD power supply

The LCD power supply block generates the row voltage

V

2

level V

M

(equivalent to

). If the LCD power supply is

switched off by AOFF = 1, then V

M

must be supplied from

an external source.

7.10

Internal reset

The internal reset circuit handles hardware and software

resets, provides the reset signal required internally and

controls the reset signal for the row driver IC.

7.11

Timing generator

The timing generator produces the various signals

required to coordinate the column driver with the row

driver.

7.12

Row driver control

The row driver IC is controlled completely by commands

from the column driver.

7.13

Column drivers and data latches

The LCD drive section includes 128

×

3 column outputs

(C0 to C383) which should be connected directly to the

LCD. The column output signals are generated in

accordance with the data in the display latches. The data

are loaded from the display RAM when the corresponding

row signal is active. Unused column outputs should be left

open-circuit when less than 384 columns are required.

INPUT

DEFAULT VALUE

CSCD

FSYN

LPOS

0

0

1

ANALOG SWITCHING0

EFFECT

AOFF = 0

AOFF = 1

analog part active

analog part switched off,

analog voltages are input

through V

COL

, V

M

------------

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF8890 | 240 + 1 outputs TFT LCD gate driver |

| PCF93C110 | 32-Bit Microcontroller |

| PCB93C110 | 32-Bit Microcontroller |

| PCG3N60C3W | TRANSISTOR | IGBT | N-CHAN | 600V V(BR)CES | CHIP |

| PCG4AX280MM | FUEHRUNGSSCHIENE LEITERPLATTE 280MM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF8833 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:STN RGB - 132 X 132 X 3 driver |

| PCF88331 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:STN RGB - 132 X 132 X 3 driver |

| PCF88332DA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:STN RGB - 132 X 132 X 3 driver |

| PCF8833U | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:STN RGB - 132 X 132 X 3 driver |

| PCF8833U/2DA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:STN RGB - 132 X 132 X 3 driver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。