- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367822 > PCK2010R (NXP Semiconductors N.V.) CK98R (100/133MHz) RCC Spread Spectrum System Clock Generator(CK98 (100/133MHz)RCC 擴(kuò)散光譜系統(tǒng)時(shí)鐘發(fā)生器) PDF資料下載

參數(shù)資料

| 型號: | PCK2010R |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | CK98R (100/133MHz) RCC Spread Spectrum System Clock Generator(CK98 (100/133MHz)RCC 擴(kuò)散光譜系統(tǒng)時(shí)鐘發(fā)生器) |

| 中文描述: | CK98R(100/133MHz)碾壓混凝土擴(kuò)頻系統(tǒng)時(shí)鐘發(fā)生器(CK98(100/133MHz)碾壓混凝土擴(kuò)散光譜系統(tǒng)時(shí)鐘發(fā)生器) |

| 文件頁數(shù): | 10/16頁 |

| 文件大小: | 101K |

| 代理商: | PCK2010R |

Philips Semiconductors

Product specification

PCK2010R

CK98R (100/133MHz) RCC spread spectrum

system clock generator

2000 May 17

10

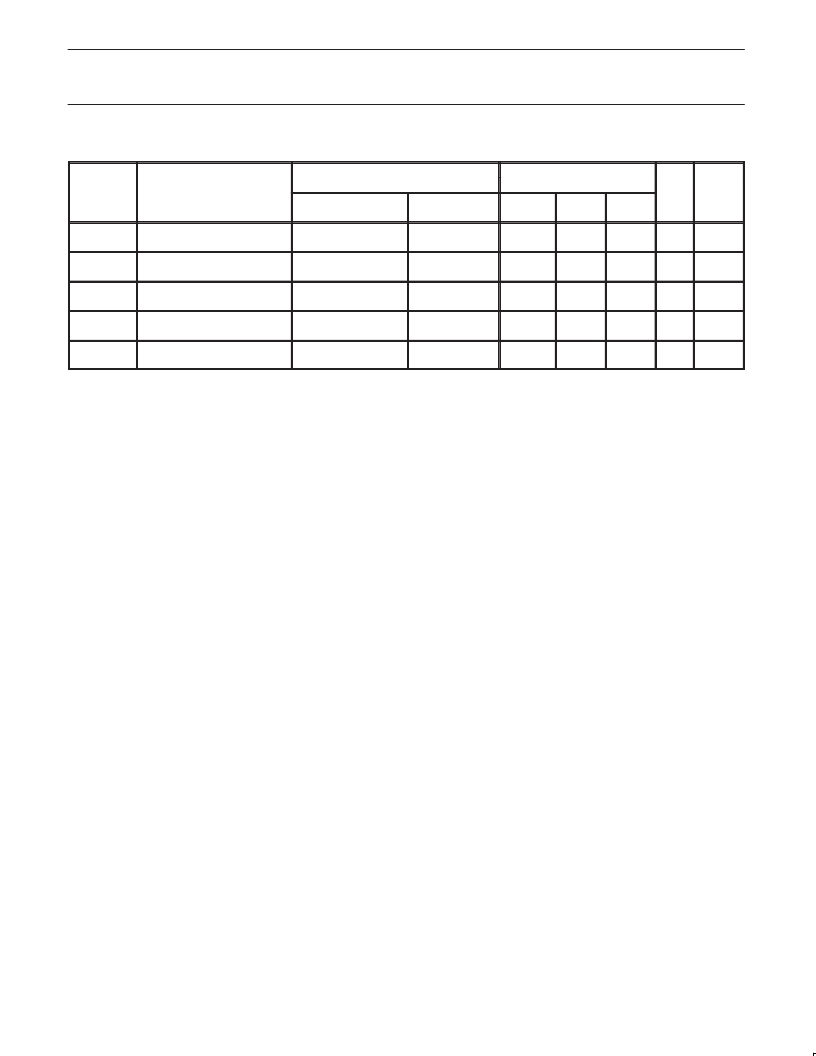

AC CHARACTERISTICS

(Continued)

TEST CONDITIONS

LIMITS

SYMBOL

PARAMETER

T

amb

= 0

°

C to +70

°

C

UNIT

NOTES

Measurement loads

(lumped)

CPU@20 pF,

3V66@30 pF

3V66@30 pF,

PCI@30 pF

CPU@20 pF,

IOAPIC@20 pF

CPU@20 pF

PCI@30 pF

CPUDIV2@20 pF

CPU@20 pF

Measure points

MIN

TYP

MAX

T

HPOFFSET

CPUCLK to 3V66 CLK,

CPU leads

3V66 CLK to PCICLK,

3V66 leads

CPUCLK to IOAPIC,

CPU leads

CPUCLK to PCICLK ,

CPU leads

CPUDIV2 to CPUCLK,

CPUDIV2 leads

CPU@1.25 V,

3V66@1.5 V

3V66@1.5 V,

PCI@1.5 V

3CPU@1.25 V,

IOAPIC@1.25 V

CPU@1.25 V

PCI@1.5 V

CPUDIV2@

CPU@1.25 V

0.0

0.45

1.5

ns

1

T

HPOFFSET

1.5

2.0

3.5

ns

1

T

HPOFFSET

1.5

2.4

4.0

ns

1

T

HPOFFSET

1.5

2.7

4.0

ns

T

HPOFFSET

0.75

1.6

2.5

ns

NOTES:

1. Output drivers must have monotonic rise/fall times through the specified V

OL

/V

OH

levels.

2. Period, jitter, offset and skew measured on rising edge @1.25 V for 2.5 V clocks and @ 1.5 V for 3.3 V clocks.

3. The PCICLK is the CPUCLK divided by four at CPUCLK = 133 MHz. The 3V66 CLK is internal VCO frequency divided by three at

CPUCLK = 100 MHz.

4. 3V66 CLK is internal VCO frequency divided by two at CPUCLK = 133 MHz. The 3V66 CLK is internal VCO frequency divided by three at

CPUCLK = 100 MHz.

5. T

HKH

is measured at 2.0 V for 2.5 V outputs, 2.4 V for 3.3 V outputs as shown in Figure 4.

6. T

HKL

is measured at 0.4 V for all outputs as shown in Figure 4.

7. The time is specified from when V

DDQ

achieves its nominal operating level (typical condition V

DDQ

= 3.3 V) until the frequency output is

stable and operating within specification.

8. T

and T

are measured as a transition through the threshold region V

= 0.4 V and V

= 2.4 V (1 mA) JEDEC specification.

9. The average period over any 1

μ

s period of time must be greater than the minimum specified period.

10.Calculated at minimum edge-rate (1V/ns) to guarantee 45/55% duty-cycle. Pulse width is required to be wider at faster edge-rate to ensure

duty-cycle specification is met.

11. Output (see Figure 5 for measure points).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCK2010 | CK98 (100/133MHz) Spread Spectrum System Clock Generator(CK98 (100/133MHz) 擴(kuò)散光譜系統(tǒng)始終發(fā)生器) |

| PCK2010DL | CK98 100/133MHz Spread Spectrum System Clock Generator |

| PCK2010RA | CK98R 100/133MHz RCC spread spectrum system clock generator |

| PCK2011 | Direct RAMbus Clock Generator(定向RAM總線時(shí)鐘發(fā)生器) |

| PCK2011DL | Direct RAMbus Clock Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCK2010RA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CK98R 100/133MHz RCC spread spectrum system clock generator |

| PCK2010RADL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CK98R 100/133MHz RCC spread spectrum system clock generator |

| PCK2010RADL,112 | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 CK98R(100/133MHZ)RCC/CLK GEN RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PCK2010RADL,118 | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 CK98R(100/133MHZ)RCC/CLK GEN RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PCK2010RDL | 制造商:PHILIPS-SEMI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。