- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄367908 > PEEL22CV10ATI-7 (Electronic Theatre Controls, Inc.) Single Resistor Gain Programmable, Precision Instrumentation Amplifier; Package: PDIP; No of Pins: 8; Temperature Range: -40°C to +85°C PDF資料下載

參數(shù)資料

| 型號(hào): | PEEL22CV10ATI-7 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類(lèi): | 測(cè)量放大器 |

| 英文描述: | Single Resistor Gain Programmable, Precision Instrumentation Amplifier; Package: PDIP; No of Pins: 8; Temperature Range: -40°C to +85°C |

| 中文描述: | 電可擦除可編程邏輯器件 |

| 文件頁(yè)數(shù): | 4/10頁(yè) |

| 文件大小: | 247K |

| 代理商: | PEEL22CV10ATI-7 |

4 of 10

04-02-009F

PEEL

TM

22CV10A

enable term will permanently enable the output buffer and

yield a dedicated output. Conversely, if every connection is

intact, the enable term will always be logically false and the

I/O will function as a dedicated input.

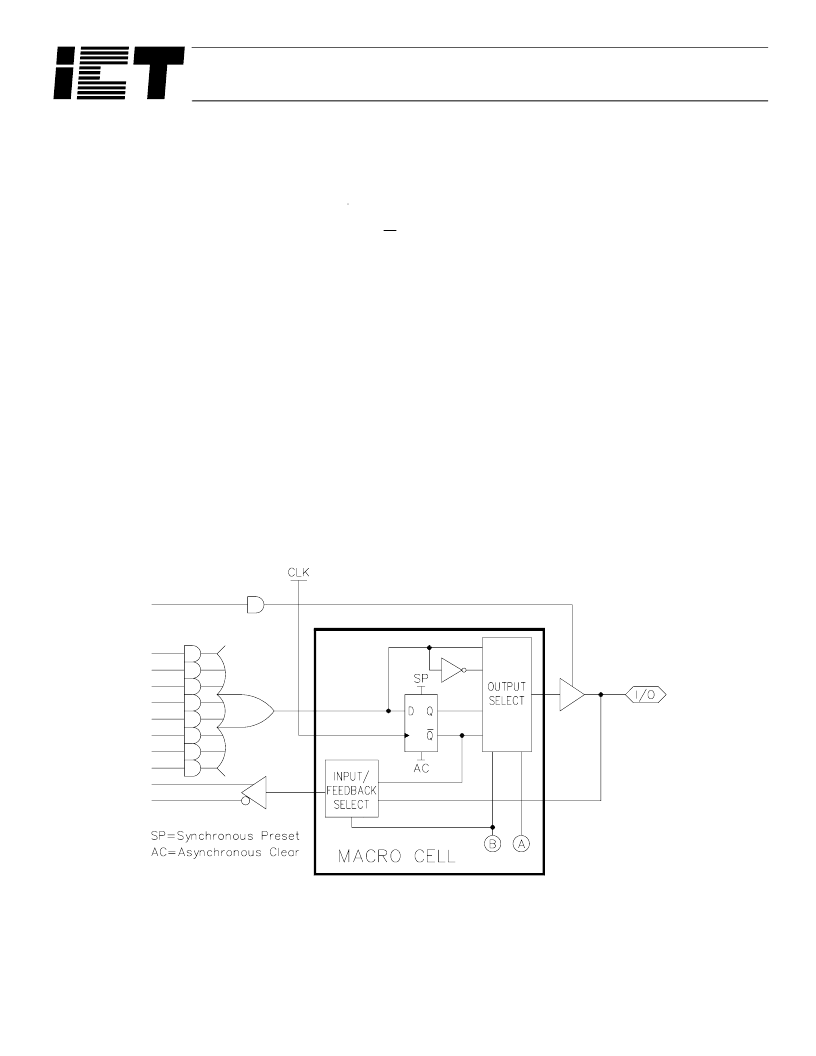

Input/Feedback Select

When configuring an I/O macrocell to implement a regis-

tered function (configurations 1 and 2 in Figure 5), the Q

output of the flip-flop drives the feedback term. When con-

figuring an I/O macrocell to implement a combinatorial

function (configurations 3 and 4 in Figure 5), the feedback

signal is taken from the I/O pin. In this case, the pin can be

used as a dedicated input or a bi-directional I/O. (Refer

also to Table 1.)

Additional Macro Cell Configurations

Besides the standard four-configuration macrocell shown in

Figure 5, each PEEL22CV10A provides an additional

eight configurations that can be used to increase design

flexibility. The configurations are the same as provided by

the PEEL18CV8 and PEEL22CV10AZ. However, to

maintain JEDEC file compatibility with standard 22V10

PLDs the additional configurations can only be utilized by

specifying the PEEL22CV10A+ for logic assembly and

programming. To reference these additional configurations

please refer to the PEEL22CV10A+ specifications at the

end of this data sheet.

Design Security

The PEEL22CV10A provides a special EEPROM secu-

rity bit that prevents unauthorized reading or copying of

designs programmed into the device. The security bit is set

by the PLD programmer, either at the conclusion of the pro-

gramming cycle or as a separate step after the device has

been programmed. Once the security bit is set, it is impos-

sible to verify (read) or program the PEEL until the entire

device has first been erased with the bulk-erase function.

Signature Word

The signature word feature allows a 24-bit code to be pro-

grammed

into

the

PEEL22CV10A

PEEL22CV10A+ software option is used. The code can

be read back even after the security bit has been set. The

signature word can be used to identify the pattern pro-

grammed into the device or to record the design revision,

etc.

if

the

Figure 4. Block Diagram of the PEEL 22CV10A I/O Macrocell.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PEEL22LV10AZJ-35 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL22LV10AZJI-25 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL22LV10AZP-35 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL22LV10AZPI-25 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL22LV10AZS-35 | CMOS Programmable Electrically Erasable Logic Device |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PEEL22CV10ATI-7L | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 12 Inp 10 I/O 7.5ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PEEL22CV10ATL-15 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Electrically-Erasable PLD |

| PEEL22CV10AZ | 制造商:ANACHIP 制造商全稱(chēng):Anachip Corp 功能描述:CMOS Programmable Electrically Erasable Logic Device |

| PEEL22CV10AZJ-25 | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 12 INP 10 I/O 25ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PEEL22CV10AZJ-25L | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 12 Input 10 I/O 25ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。