- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369992 > PEELTM16CV8J-25 ASIC PDF資料下載

參數(shù)資料

| 型號: | PEELTM16CV8J-25 |

| 英文描述: | ASIC |

| 中文描述: | 專用集成電路 |

| 文件頁數(shù): | 3/10頁 |

| 文件大小: | 173K |

| 代理商: | PEELTM16CV8J-25 |

3

04-02-004I

PEEL

TM

16CV8

VC C

Simple Mode

1

VC C

Simple Mode

2

Simple Mode

3

Programmable Macrocell

The macrocell provides complete control over the architecture of each

output. The ability to configure each output independently permts users

to tailor the configuration of the PEEL

TM

16CV8 to the precise require-

ments of their designs.

Macrocell Architecture

Each macrocell consists of an OR function, a D-type flip-flop, an output

polarity selector, and a programmable feedback path. Four EEPROM

architecture bits MS0, MS1, OP, and RC control the configuration of

each macrocell. Bits MS0 and MS1 are global, and select between Sim-

ple, Complex, and Registered mode for the whole device. Bits OP and

RC are local for each macrocell; bit OP controls the output polarity and

bit RC selects between registered and combinatorial operation and also

specifies the feedback path. Table 2 shows the architecture bit settings

for each possible configuration.

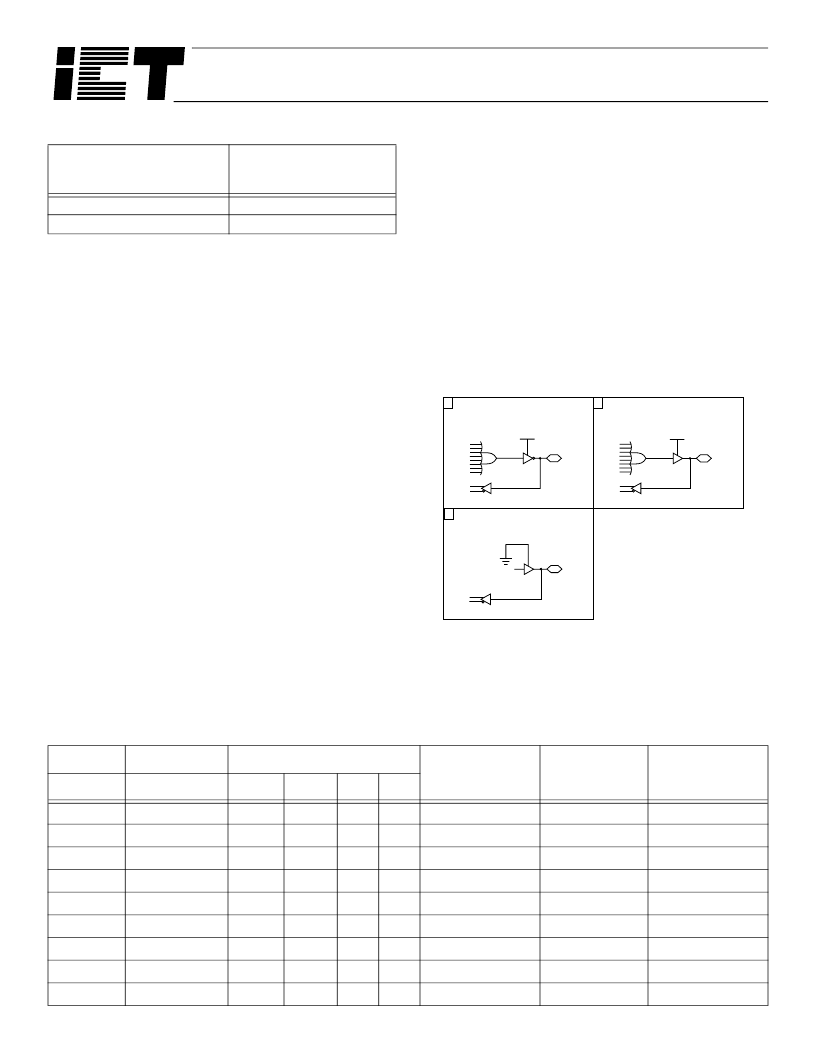

Equivalent circuits for the possible macrocell configurations are illus-

trated in Figures 3, 4, and 5. When creating a PEEL

TM

device design,

the desired macrocell configuration generally is specified explicitly in the

design file. When the design is assembled or compiled, the macrocell

configuration bits are defined in the last lines of the JEDEC program-

mng file.

16RP6

Registered

14RP8

Registered

Table 1 : PEEL

TM

16CV8 Device Compatibility

PLD Architecture

Compatibility

PEEL

TM

16CV8

Device Mode

Simple Mode

In Simple mode, all eight product terms feed the OR array which can

generate a purely combinatorial function for the output pin. The pro-

grammable output polarity selector allows active-high or active-low logic,

elimnating the need for external inverters. For output functions, the

buffer can be permanently enabled. Feedback into the array is available

on all macrocell I/O pins, except for pins 15 and 16. Figure 6 shows the

logic array of the PEEL

TM

16CV8 configured in Simple mode.

Simple mode also provides the option of configuring an I/O pin as a ded-

icated input. In this case, the output buffer is permanently disabled, and

the I/O pin feedback is used to bring the input signal fromthe pin into the

logic array. This option is available for all I/O pins except pins 15 and 16.

Figure 3 shows the possible Simple mode macrocell configurations.

Figure 3 - Macrocell Configurations for Simple mode of the PEEL

TM

16CV8 (see Figure 6 for Logic Array)

Table 2 : PEEL

TM

16CV8 Device Mode/Macrocell Configuration Bits

Config.

Mode

Architecture Bits

Function

Polarity

Feedback

#

MSO

MS1

OP

RC

1

Simple

1

0

0

0

Combinatorial

Active Low

I/O Pin

2

Simple

1

0

1

0

Combinatorial

Active High

I/O Pin

3

Simple

1

0

X

1

None

None

I/O Pin

1

Complex

1

1

0

1

Combinatorial

Active Low

I/O Pin

2

Complex

1

1

1

1

Combinatorial

Active High

I/O Pin

1

Registered

0

1

0

0

Registered

Active Low

Registered

2

Registered

0

1

1

0

Registered

Active High

Registered

3

Registered

0

1

0

1

Combinatorial

Active Low

I/O Pin

4

Registered

0

1

1

1

Combinatorial

Active High

I/O Pin

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PEELTM16CV8P-25 | Low Noise Very High Speed Operational Amplifier; Package: SO; No of Pins: 8; Temperature Range: 0°C to +70°C |

| PEELTM16CV8S-25 | ASIC |

| PEELTM16CV8T-25 | 140MHz Video Current Feedback Amplifier; Package: SO; No of Pins: 8; Temperature Range: 0°C to +70°C |

| PEF-03A-1500B | 100MHz Current Feedback Amplifier with DC Gain Control; Package: PDIP; No of Pins: 8; Temperature Range: 0°C to +70°C |

| PEF-03A-500B | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PEELTM16CV8P-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| PEELTM16CV8S-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| PEELTM16CV8T-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| P-EESB5 | 制造商:Panasonic Industrial Company 功能描述:SENSOR |

| PEF | 制造商:Infineon Technologies AG 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。