- 您現在的位置:買賣IC網 > PDF目錄370005 > PLL1706 RS232/EIA562/RS485 Transceivers; Package: PDIP; No of Pins: 24; Temperature Range: -40°C to +85°C PDF資料下載

參數資料

| 型號: | PLL1706 |

| 英文描述: | RS232/EIA562/RS485 Transceivers; Package: PDIP; No of Pins: 24; Temperature Range: -40°C to +85°C |

| 中文描述: | 3.3伏雙PLL的多時鐘發(fā)生器 |

| 文件頁數: | 10/17頁 |

| 文件大小: | 128K |

| 代理商: | PLL1706 |

PLL1705

PLL1706

SLES046A

–

AUGUST 2002

–

REVISED SEPTEMBER 2002

www.ti.com

10

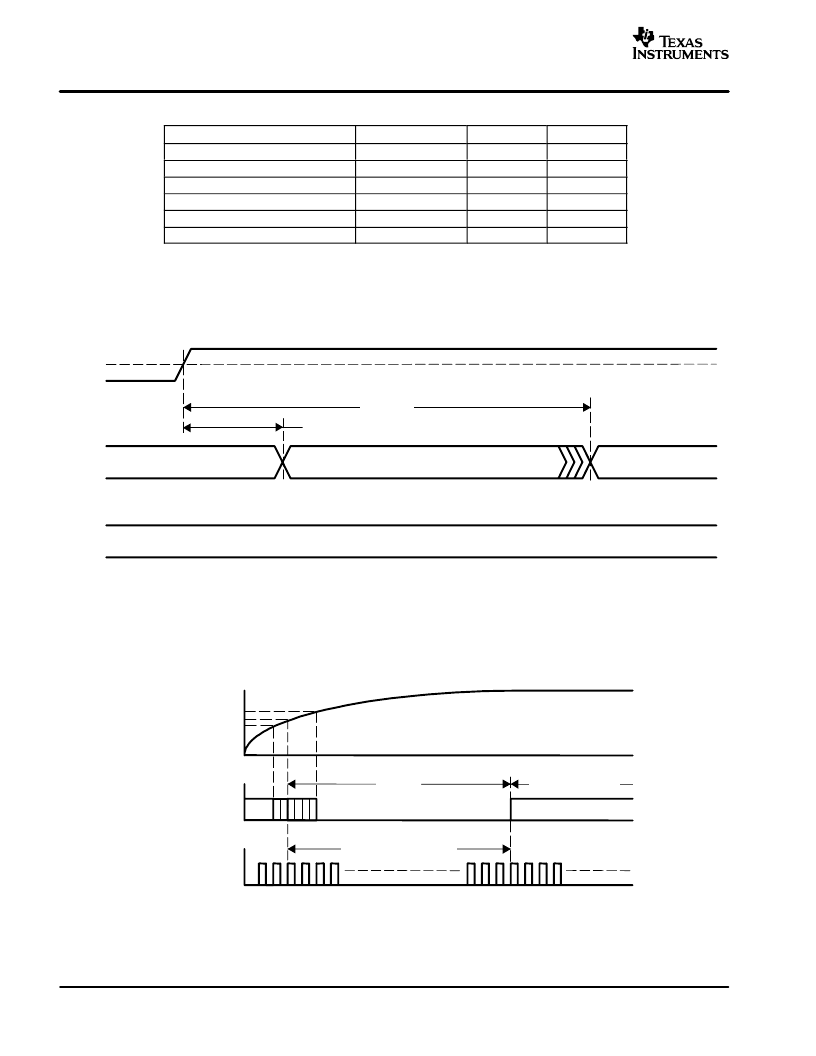

Table 3. Sampling Frequencies and System Clock Output Frequencies

SAMPLING FREQUENCY (kHz)

32

44.1

48

64

88.2

96

SAMPLING RATE

Standard

Standard

Standard

Double

Double

Double

SCKO2 (MHZ)

8.192

11.2896

12.288

16.384

22.5792

24.576

SCKO3 (MHZ)

12.288

16.9344

18.432

24.576

33.8688

36.864

Response time from power on (or applying the clock to XT1) to SCKO settling time is typically 3 ms. Delay time from

sampling frequency change to SCKO settling is 200 ns maximum. This clock transient timing is not synchronized with the

SCKOx signals. Figure 10 illustrates SCKO transient timing in the PLL1706. External buffers are recommended on all

output clocks in order to avoid degrading the jitter performance of the PLL1705/6.

SCKO0

SCKO1

200 ns

SCKO2

SCKO3

ML

Stable

Clock Transition Region

Stable

33.8688 MHz, 384 or 768 of 44.1 kHz

1

–

2 Clocks of MCKO1,2

Figure 10. System Clock Transient Timing

POWER-ON RESET

The PLL1705/6 has an internal power-on reset circuit. The mode register of PLL1706 is initialized with default settings by

power-on reset. Throughout the reset period, all clock outputs are enabled with the default settings after power up time.

Initialization by internal power-on reset is done automatically during 1024 master clocks at V

DD

> 2.0 V (TYP). Power-on

reset timing is shown in Figure 11.

Reset

Reset Removal

1024 Master Clocks

VDD

2.4 V

2.0 V

1.6 V

Internal Reset

Master Clock

Figure 11. Power-On Reset Timing

相關PDF資料 |

PDF描述 |

|---|---|

| PLL1810A | RS232/EIA562/RS485 Transceivers; Package: PDIP; No of Pins: 24; Temperature Range: -40°C to +85°C |

| PLL2001P | Serial-Input Frequency Synthesizer |

| PLL2013X | PLL2013X 20MHZ~170MHZ FSPLL PLL2013X|Data Sheet |

| PLL2014X | 8-Channel Analog Multiplexer with Cascadable Serial Interface; Package: SSOP; No of Pins: 16; Temperature Range: 0°C to +70°C |

| PLL2026X | 8-Channel Analog Multiplexer with Cascadable Serial Interface; Package: PDIP; No of Pins: 16; Temperature Range: 0°C to +70°C |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PLL1706DBQ | 功能描述:時鐘發(fā)生器及支持產品 3.3 V Dual PLL Multi Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1706DBQG4 | 功能描述:時鐘發(fā)生器及支持產品 3.3V Dual PLL Multi- Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1706DBQR | 功能描述:時鐘發(fā)生器及支持產品 3.3V Dual PLL Multi- Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1706DBQRG4 | 功能描述:時鐘發(fā)生器及支持產品 3.3V Dual PLL Multi- Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1707 | 制造商:BB 制造商全稱:BB 功能描述:3.3 V DUAL PLL MULTICLOCK GENERATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。