- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370007 > PLS159AA (NXP SEMICONDUCTORS) Programmable logic sequencer 16 】 45 】 12 PDF資料下載

參數(shù)資料

| 型號: | PLS159AA |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | PLD |

| 英文描述: | Programmable logic sequencer 16 】 45 】 12 |

| 中文描述: | OT PLD, 35 ns, PQCC20 |

| 封裝: | PLASTIC, LCC-20 |

| 文件頁數(shù): | 6/12頁 |

| 文件大小: | 132K |

| 代理商: | PLS159AA |

Philips Semiconductors Programmable Logic Devices

Product specification

PLS159A

Programmable logic sequencer

(16

×

45

×

12)

October 22, 1993

30

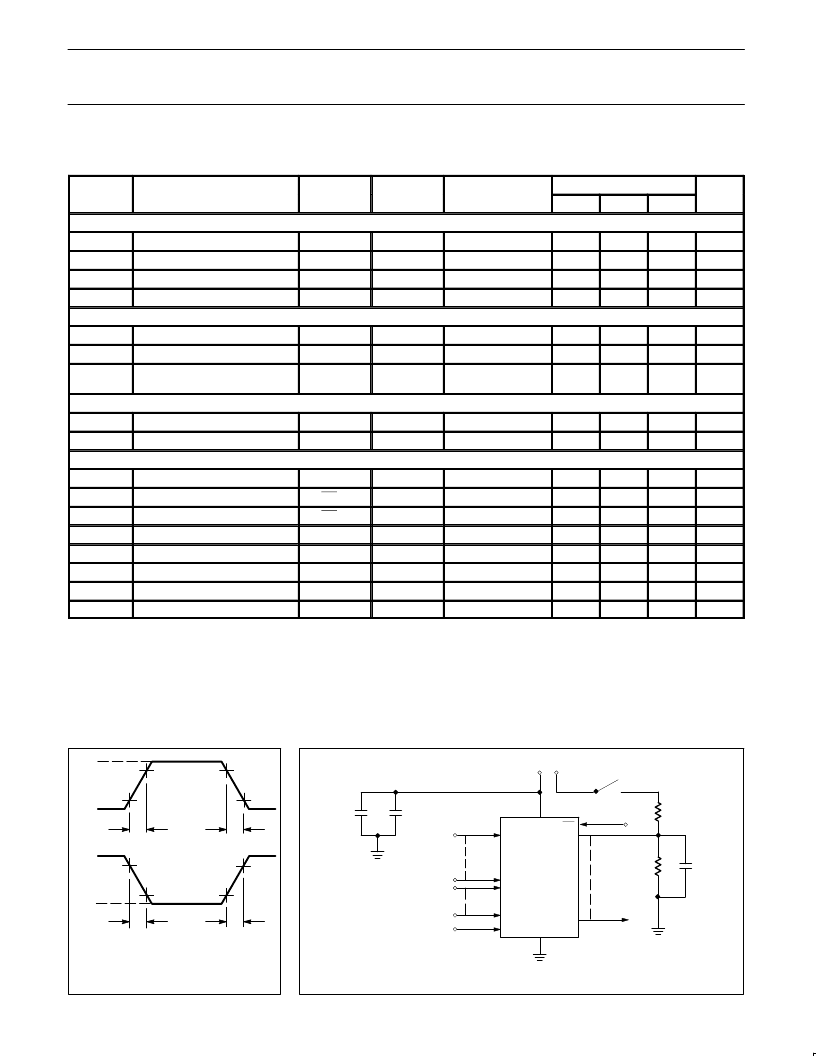

AC ELECTRICAL CHARACTERISTICS

0

°

C

≤

T

amb

≤

+75

°

C, 4.75V

≤

V

CC

≤

5.25V, R

1

=470

, R

2

= 1k

LIMITS

TYP

1

SYMBOL

PARAMETER

FROM

TO

TEST CONDITION

MIN

MAX

UNIT

Pulse width

t

CKH

t

CKL

t

CKP

t

PRH

Setup time

5

Clock

2

High

CK +

CK –

C

L

= 30pF

C

L

= 30pF

C

L

= 30pF

C

L

= 30pF

20

15

ns

Clock Low

CK –

CK +

20

15

ns

Period

CK +

CK +

55

45

ns

Preset/Reset pulse

(I,B) –

(I,B) +

35

30

ns

t

IS1

t

IS2

Input

(I,B)

±

F

±

CK +

C

L

= 30pF

C

L

= 30pF

35

30

ns

Input (through F

n

)

Input (through

Complement Array)

4

CK +

15

10

ns

t

IS3

(I,B)

±

CK +

C

L

= 30pF

55

45

ns

Hold time

t

IH1

t

IH2

Propagation delay

Input

(I,B)

±

F

±

CK +

C

L

= 30pF

C

L

= 30pF

0

–5

ns

Input (through F

n

)

CK +

15

10

ns

t

CKO

t

OE1

t

OD1

t

PD

t

OE2

t

OD2

t

PRO

t

PPR

Clock

Output enable

3

Output disable

3

CK +

F

±

C

L

= 30pF

C

L

= 30pF

C

L

= 5pF

C

L

= 30pF

C

L

= 30pF

C

L

= 5pF

C

L

= 30pF

C

L

= 30pF

15

20

ns

OE –

F –

20

30

ns

OE +

F +

20

30

ns

Output

Output enable

3

Output disable

3

(I,B)

±

B

±

B

±

25

35

ns

(I,B) +

20

30

ns

(I,B) –

B +

20

30

ns

Preset/Reset

(I,B) +

F

±

35

45

ns

Power-on/preset

V

CC

+

F –

0

10

ns

NOTES:

1. All typical values are at V

= 5V, T

= +25

°

C.

2. To prevent spurious clocking, clock rise time (10% – 90%)

≤

10ns.

3. For 3-State output; output enable times are tested with C

L

= 30pF to the 1.5V level, and S

1

is open for high-impedance to High tests and

closed for high-impedance to Low tests. Output disable times are tested with C

L

= 5pF. High-to-High impedance tests are made to an output

voltage of V

T

= (V

OH

– 0.5V) with S

1

open, and Low-to-High impedance tests are made to the V

T

= (V

OL

+ 0.5V) level with S

1

closed.

4. When using the Complement Array t

CKP

= 75ns (min).

5. Limits are guaranteed with 12 product terms maximum connected to each sum term line.

VOLTAGE WAVEFORMS

MEASUREMENTS:

All circuit delays are measured at the +1.5V level

of inputs and outputs, unless otherwise specified.

90%

10%

5ns

5ns

5ns

5ns

90%

10%

+3.0V

+3.0V

0V

0V

t

R

t

F

Input Pulses

TEST LOAD CIRCUIT

+5V

C

L

R

1

R

2

S

1

GND

B

Z

B

Y

INPUTS

I

0

I

n

B

W

B

X

CLK

OUTPUTS

C

2

C

1

DUT

NOTE:

C

1

and C

2

are to bypass V

CC

to GND.

V

CC

OE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PLS159AN | Programmable logic sequencer 16 】 45 】 12 |

| PLS173A | Programmable logic array 22 】 42 】 10 |

| PLS173N | Programmable logic array 22 】 42 】 10 |

| PLS179A | Fuse-Programmable PLD |

| PLS179N | High Speed, 16-Bit, 500ksps Sampling A/D Converter with Shutdown; Package: SSOP; No of Pins: 36; Temperature Range: 0°C to +70°C |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PLS159AF | 制造商:NXP Semiconductors 功能描述: |

| PLS159AN | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Programmable logic sequencer 16 】 45 】 12 |

| PLS159AN-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fuse-Programmable PLD |

| PLS167/BLA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fuse-Programmable PLD |

| PLS167-33 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:24-PIN TTL/CMOS PROGRAMMABLE LOGIC SEQUENCERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。