- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378055 > PM7326-BI (PMC-SIERRA INC) ATM/PACKET TRAFFIC MANAGER AND SWITCH PDF資料下載

參數(shù)資料

| 型號: | PM7326-BI |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/PACKET TRAFFIC MANAGER AND SWITCH |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA352 |

| 封裝: | 35 X 35 MM, 1.45 MM HEIGHT, SBGA-352 |

| 文件頁數(shù): | 1/2頁 |

| 文件大小: | 65K |

| 代理商: | PM7326-BI |

PM7326

PMC-Sierra,Inc.

ATM/PACKET Traffic Manager and Switch

S/UNI-APEX

PMC-990146 (P2)

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS

’

INTERNAL USE

1999 PMC-Sierra, Inc.

C

C

C

C

C

C

C

C

T

T

T

T

Processor

Interface

LRSX

LRSOP

LRDAT[15:0]

LRPRTY

LRENB

LRADR[5:0]

LRPA

Loop Rx

Any-PHY

T

S

LRCLK

WRSX

WRSOP

WRDAT[15:0]

WRPRTY

WRENB

WRADR[2:0]

WRPA

WAN Rx

Any-PHY

WRCLK

R

O

C

C

C

C

C

C

SSRAM Interface

LTSX

LTSOP

LTDAT[15:0]

LTPRTY

LTENB

LTADR[11:0]

LTPA

Loop Tx

Any-PHY

LTCLK

WTSX

WTSOP

WTDAT[15:0]

WTPRTY

WTENB

WTADR[2:0]

WTPA

WAN Tx

Any-PHY

WTCLK

JTAG Test

Access Port

SDRAM Interface

AD[31:0]

Ctrl Lines

Que Management &

Scheduling

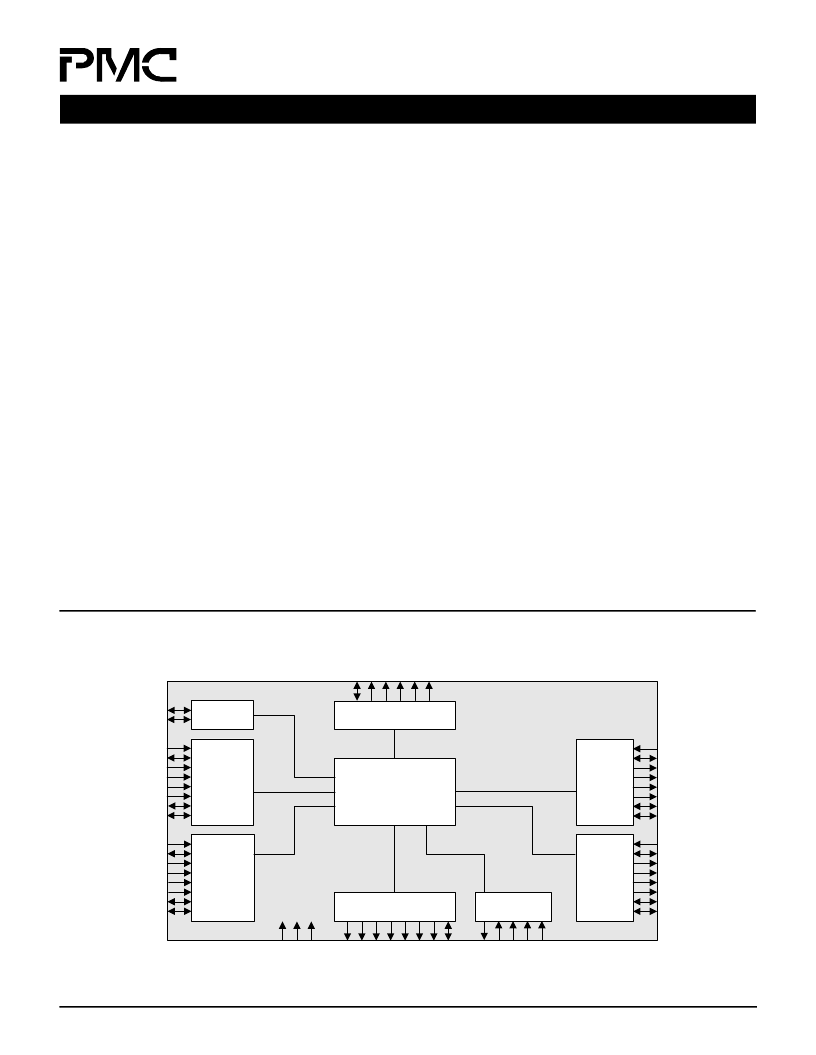

BLOCK DIAGRAM

FEATURES

ATM (fixed length cell) and packet/

frame traffic manager and switch.

2048 line ports, 4 WAN ports, and a

high speed microprocessor port. Any

port to any port switching for 64k

independent connections.

Manages up to 256k cell (16M byte)

data buffer and 4M byte context

memory shared over all ports.

Configurable progressive throttling of

buffer consumption, with memory

reservation under high consumption.

Supports ABR with EFCI marking.

Buffer congestion controlled via Partial

Packet Discard, Early Packet Discard

(PPD/EPD). Cell at a time discard also

supported.

For frame/packet flows:

Supports external wire speed HDLC

processor, SAR, and flow classifier

via packet-contiguous queuing and

scheduling.

Error indication in AAL5 EOM trailer

(set by SAR or classifier) can invoke

errored packet discard, thereby

eliminating need for packet buffers

in external devices.

Traffic queuing algorithm is highly

configurable on a per connection, per

class, and per port basis.

Configurable scheduling of 4 classes

of service on every port, with rate

shaping available for the 4 WAN ports.

Configurable traffic parameters

enabling a mix of CBR, VBR, GFR,

and UBR classes.

Configurable OAM cell queuing and

special handling on all ports.

VPI/VCI header mapping.

Supports 700 Mb/s ingress traffic and

700 Mb/s egress traffic aggregated

across all ports.

Low power 3.3/2.5V CMOS.

Standard 5 pin P1149 JTAG port.

352 ball SBGA, 35mm x 35mm.

BUS INTERFACES

8/16 bit, 52 MHz UTOPIA L2 bus.

Line side:

Enhanced UTOPIA Tx master

supports 2048 ports. Rx master

supports 32 ports.

Or single port slave.

WAN side:

Master (with optional cell length

expansion) supports 4 Tx or Rx

ports.

Or single port slave.

MICROPROCESSOR INTERFACE

66 MHz, 32 bit address/data bus

capable of single or burst access to

internal registers and cell buffers.

Supports cell/packet transfer to/from

any port, with CRC32 and CRC10

calculation supported in hardware.

Works seamlessly with

S/UNI-VORTEX and S/UNI-DUPLEX

to implement a system-wide

embedded communication channel.

CONGESTION CONTROL

Traffic discard thresholds configurable

per connection (independent CLP0

and CLP1 thresholds), per class, per

port, and per direction.

Guaranteed Frame Rate (GFR)

implemented via CLP0 minimum buffer

size reservation per connection.

QUEUING & SCHEDULING

64k traffic staging queues (one per

connection) individually assignable to

any CoS on any port.

8k + 20 scheduling queues: 4 CoS

queues per port, 2048 line ports, 4

WAN ports, and 1 processor port.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7328 | ATM Layer Solution |

| PM7328-BI | ATM LAYER SOLUTION |

| PM7329-BI | ATM TRAFFIC MANAGER AND SWITCH |

| PM7329 | ATM TRAFFIC MANAGER AND SWITCH |

| PM7339 | Quad Cell Delineation Block Device |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM7328 | 制造商:PMC 制造商全稱:PMC 功能描述:ATM LAYER SOLUTION |

| PM7328-BI | 制造商:PMC 制造商全稱:PMC 功能描述:ATM LAYER SOLUTION |

| PM7329 | 制造商:PMC 制造商全稱:PMC 功能描述:Packet/ATM Traffic Manager and Switch |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。