- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378056 > PM7388 (PMC-SIERRA INC) Frame Engine and Datalink Manager PDF資料下載

參數(shù)資料

| 型號: | PM7388 |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Frame Engine and Datalink Manager |

| 中文描述: | 8 CHANNEL(S), 52M bps, SERIAL COMM CONTROLLER, PBGA520 |

| 封裝: | 40 X 40 MM, 1.54 MM HEIGHT, 1.27 MM PITCH, THERMALLY ENHANCED, BGA-520 |

| 文件頁數(shù): | 1/2頁 |

| 文件大?。?/td> | 58K |

| 代理商: | PM7388 |

PM7388

Preliminary

Frame Engine and Datalink Manager

FREEDM 336A1024

PMC-1991475 (p2)

PROPRIETARY AND CONFIDENTIAL TO PMC

-

SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

Copyright PMC

-

Sierra, Inc. 2001

FEATURES

Single-chip multi-channel packet

processor supporting line rate

throughput transfers of packet sizes

from 40 to 9.6 Kbytes, for up to an

aggregate of 336 T1s, 252 E1s, or 12

DS-3s.

Provides simultaneous support of

PPP, Frame Relay, Multilink-PPP and

Multilink-Frame Relay protocols.

Alternative protocols supported via

HDLC termination and full packet store

of the data within the HDLC structure.

MULTILINK PPP AND FRAME

RELAY BUNDLES

Capable of supporting fragment sizes

from 1 to 9.6 Kbytes.

Support for 3 egress fragmentation

sizes (128, 256, and 512 bytes)

configurable on a per multilink bundle.

Optionally full packet transfers are

supported on a per bundle basis.

Supports up to 168 multilink bundles

with up to 12 member links per bundle.

These bundles are composed of

independent HDLC channels.

Support for up to 100 ms of intra

bundle skew in the receive direction

when supporting the minimum.

fragment size.

Support for PPP header compression

as per RFC 1661.

PPP

Support for 16 COS levels in

accordance with RFC 2686.

Either 12 bit or 24 bit sequence

number, with short and long fragment

header formats, is supported.

Link Control protocol packets are

identified by the PID as control

protocols and will be forwarded to the

Any-PHY interface.

FRAME RELAY

Link layer address lookup can be

performed based on HDLC channel

and 10 bit DLCI for HDLC channels

supporting Frame Relay protocols.

The lookup algorithm can support a

maximum of 16 K connection

identifiers (CIs) amongst multilink FR

bundles. The connection identifiers

are ignored in singlelink FR channels.

Control frames are identified and

forwarded to Any-PHY interface.

12 bit sequence numbers supported.

FECN, BECN, and DE ingress

processing as per FRF.12.

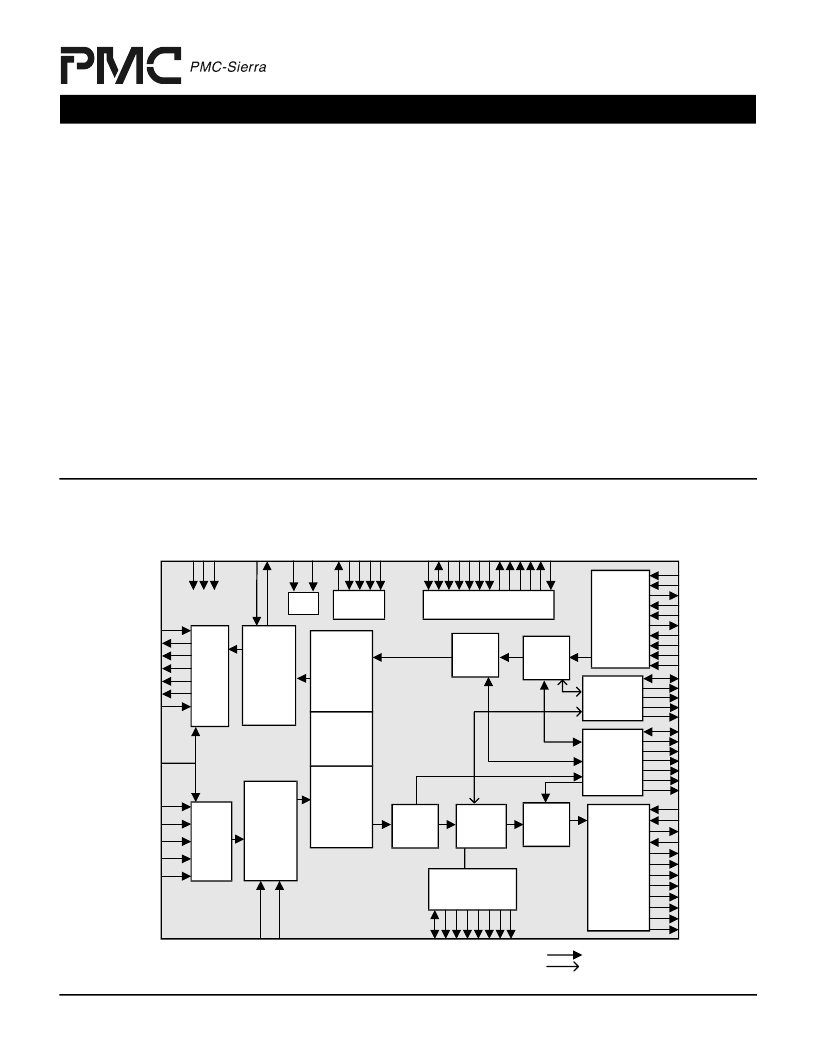

Rx ANY-PHY

I/F

(RAPI-12)

RXCLK

RXADDR[3:0]

RVAL

RSX

RSOP

REOP

RMOD

RERR

RXDATA[15:0]

RXPRTY

RENB

RPA

SRAM

Controller

(SRAMC)

CCDAT[35:0]

CCADD[17:0]

CCBSELB[1:0]

CCWEB

CCSELB

CB DRAM

Controller

(CB_DRAMC)

CBDAT[47:0]

CBADD[12:0]

CBRASB

CBCASB

CBBS[1:0]

CBWEB

CBCSB

Microprocessor I/F (BUMP2)

A

R

B

C

I

W

B

A

W

B

B

I

B

Tx

Fragment

Builder

(TFRAG)

Tx ANY-PHY

I/F (TAPI-12)

TXCLK

TXADDR[15:0]

TEOP

TMOD

TERR

TRDY

TSX

TXPRTY

TXDATA[15:0]

TPA

Egress

Queue

Manager

(EQM-12)

Ingress

Queue

Manager

(EQM-12)

Frame

Builder

(FRMBLD)

Rx

Fragment

Builder

(RFRAG)

RS DRAM

Controller

(RS_DRAMC)

R

R

R

R

R

D

R

R

Rx HDLC

Processor /

Partial Packet

Buffer

(RHDL-12)

Performance

Monitor

(PM-12)

Extract

SBI

(EXSBI-

336)

DC1FP

DV5

DPL

DDP

DDATA[7:0]

Tx HDLC

Processor /

Partial Packet

Buffer

(THDL-12)

Receive

Channel

Assigner

(RCAS-12)

R

T

T

JTAG

T

T

T

T

T

Insert

SBI

(INSBI-

336)

AJUST_REQ

AV5

APL

ADP

ADATA[7:0]

CIFPOUT

ACIFP

Transmit

Channel

Assigner

(TCAS-12)

REFCLK

Data

Control

DDLL-

140

S

R

S

P

R

D

BLOCK DIAGRAM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7389 | Frame Engine and Datalink Manager |

| PM7800 | Digital Correction Signal Processor |

| PM7830 | Baseband Radio Interface Controller |

| PM8172 | PM8172 System Controller |

| PM8310 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM7389 | 制造商:PMC 制造商全稱:PMC 功能描述:Frame Engine and Datalink Manager |

| PM7389-BI | 制造商:Rochester Electronics LLC 功能描述: 制造商:PMC-Sierra 功能描述:Electronic Component |

| PM7389-BI-P | 制造商:PMC-Sierra 功能描述:Electronic Component |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。