- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368149 > PSD402A1-20UI 100V 100kRad Hi-Rel Single N-Channel TID Hardened MOSFET in a SMD-2 package; Similar to IRHNA7160 with optional Total Dose Rating of 500kRads PDF資料下載

參數(shù)資料

| 型號(hào): | PSD402A1-20UI |

| 英文描述: | 100V 100kRad Hi-Rel Single N-Channel TID Hardened MOSFET in a SMD-2 package; Similar to IRHNA7160 with optional Total Dose Rating of 500kRads |

| 中文描述: | 現(xiàn)場(chǎng)可編程外圍 |

| 文件頁(yè)數(shù): | 94/123頁(yè) |

| 文件大?。?/td> | 657K |

| 代理商: | PSD402A1-20UI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)當(dāng)前第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

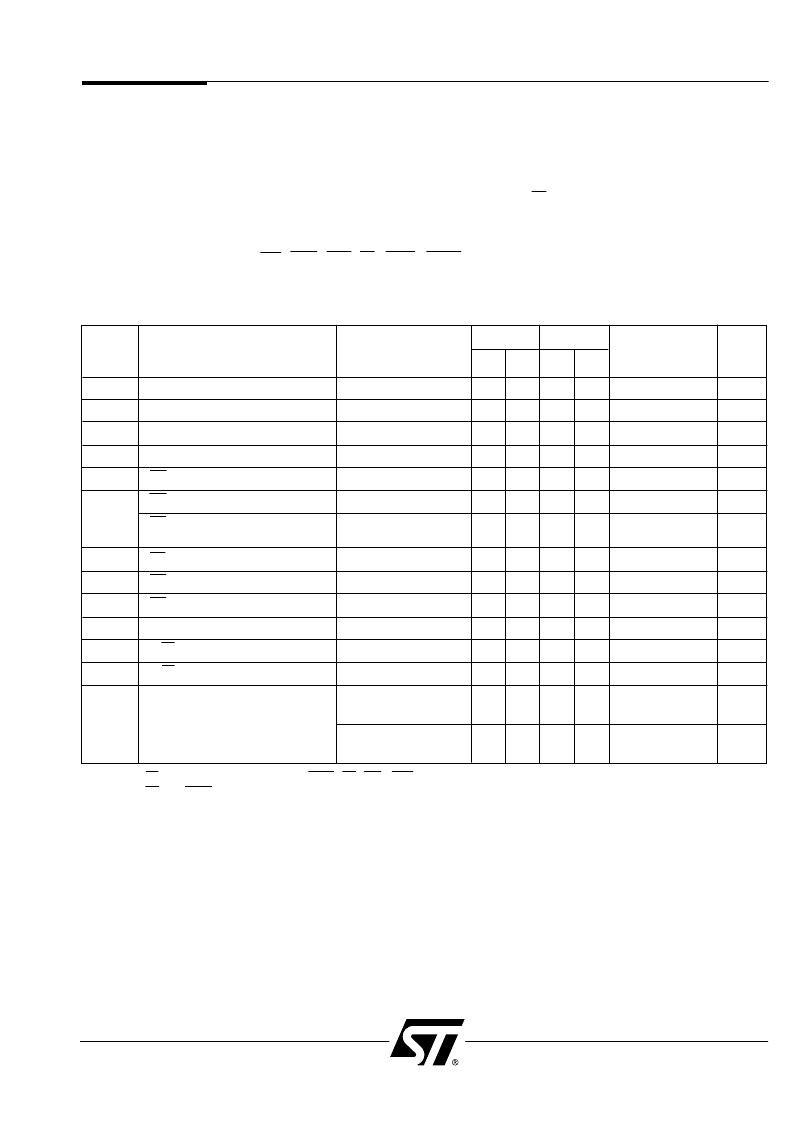

PSD4XX Famly

91

-20

-25

EPROM_CMiser

ON

Symbol

t

LVLX

t

AVLX

t

LXAX

t

AVQV

t

SLQV

Parameter

Conditions

Min Max Min Max

Unit

ALE or AS Pulse Width

30

30

0

ns

Address Setup Time

(Note 3)

12

15

0

ns

Address Hold Time

(Note 3)

12

17

0

ns

Address Valid to Data Valid

(Note 3)

200

250

Add 20

ns

CS Valid to Data Valid

200

275

Add 20

ns

RD to Data Valid 8/16-Bit Bus

(Note 1)

50

80

0

ns

t

RLQV

RD to Data Valid 8-Bit Bus,

8031 Separate Mode

(Note 2)

57

90

0

ns

t

RHQX

t

RLRH

t

RHQZ

t

EHEL

t

THEH

t

ELTL

RD Data Hold Time

(Note 1)

0

0

0

ns

RD Pulse Width

(Note 1)

40

70

0

ns

RD to Data High-Z

(Note 1)

45

45

0

ns

E Pulse Width

40

70

0

ns

R/W Setup Time to Enable

20

15

0

ns

R/W Hold Time After Enable

0

0

0

ns

In 16-Bit Data Bus

Mode (Note 4)

Address Input Valid to

Address Output Delay

40

60

0

ns

t

AVPV

In 8-Bit Data Bus

Mode (Note 4)

50

60

0

ns

Read Timng

(3.0 V ± 10%)

Explanation of AC Symbols for Non ZPLD Timing.

Example:

t

AVLX

Time from Address Valid to ALE Invalid.

A

– Address

C

– Power Down

D

– Input Data

E

– E

H

– Logic Level High

I

– Interrupt

L

– Logic Level Low or ALE

N

– Reset

P

– Port Signal

Q

– Output Data

R

– WR, UDS, LDS, DS, IORD, PSEN

S

– Chip Select

T

– R/W

t

– Time

V

– Valid

X

– No Longer a Valid Logic Level

Z

– Float

13.11 Microcontroller Interface – AC/DC Parameters (ZPSD4XXV Versions)

(3.0 V ± 10%)

NOTES:

1. RD timing has the same timing as PSEN, DS, LDS, UDS signals.

2. RD and PSEN have the same timing for 8031 mode.

3. Any input used to select an internal PSD4XX function.

4. In multiplexed mode latched address generated from ADIO delay to address output on any Port.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD402A1-70J | 100V 100kRad Hi-Rel Single N-Channel TID Hardened MOSFET in a SMD-2 package; Similar to IRHNA7160 with optional Total Dose Rating of 1000kRads |

| PSD402A1-70U | Field-Programmable Peripheral |

| PSD402A1-90J | 100V 100kRad Hi-Rel Single N-Channel TID Hardened MOSFET in a SMD-2 package; JANS Certified version of the IRHNA7160 |

| PSD402A2-20UI | 200V 100kRad Hi-Rel Single N-Channel TID Hardened MOSFET in a Low-Ohmic TO-254AA package. Also available with Total Dose Rating of 300kRads.; Similar to IRHMS67260 with optional Total Dose Rating of 300kRads |

| PSD402A2-70J | 200V 100kRad Hi-Rel Single N-Channel TID Hardened MOSFET in a Low-Ohmic TO-254AA package. Also available with Total Dose Rating of 300kRads.; A IRHMS67260 with Standard Packaging |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD402A1-70J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD402A1-70U | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD402A1-90J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD402A1-90U | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD402A1-C-15J | 制造商:WSI 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。