- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368226 > PSD4235G3-A-15JI (意法半導(dǎo)體) CAP 0.68UF 20V 10% TANT SMD-3216-18 TR-13-PL GOLD PDF資料下載

參數(shù)資料

| 型號: | PSD4235G3-A-15JI |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | CAP 0.68UF 20V 10% TANT SMD-3216-18 TR-13-PL GOLD |

| 中文描述: | Flash在系統(tǒng)可編程外設(shè)的16位微控制器 |

| 文件頁數(shù): | 54/89頁 |

| 文件大小: | 703K |

| 代理商: | PSD4235G3-A-15JI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當(dāng)前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

PSD4235G2

54/89

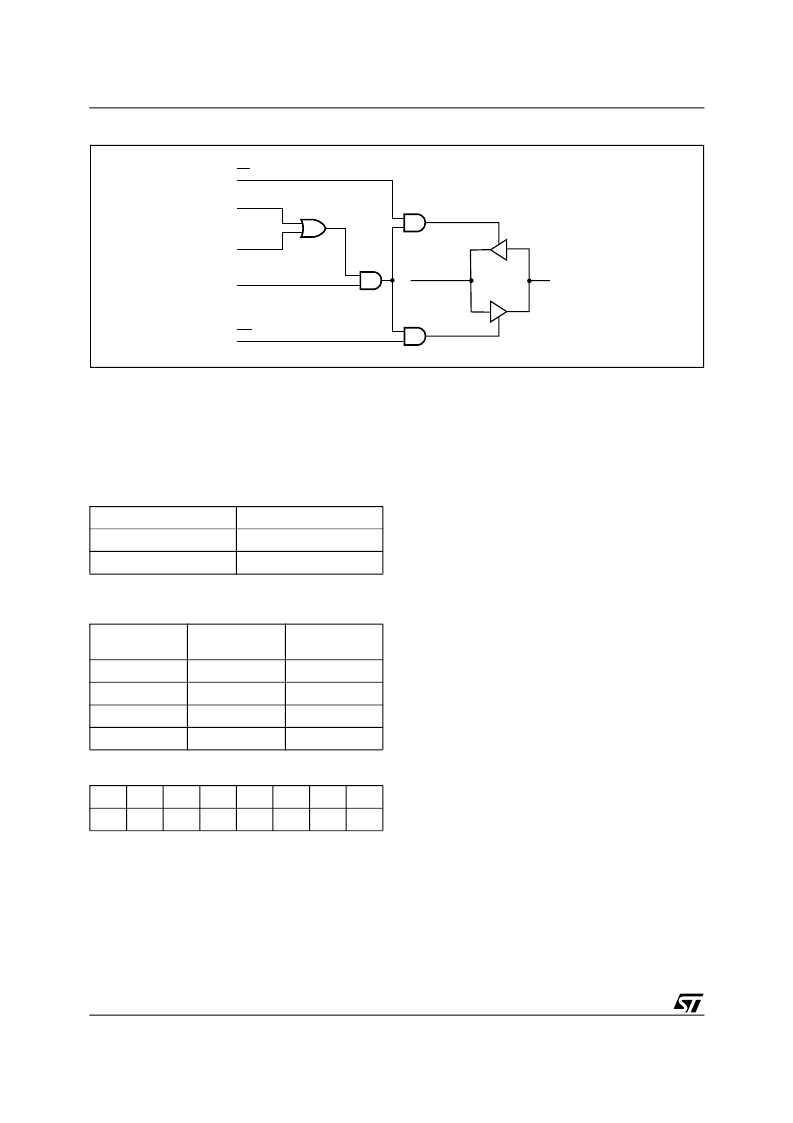

Figure 28. Peripheral I/O Mode

Direction Register.

The Direction Register con-

trols the direction of data flow in the I/O Ports. Any

bit set to 1 in the Direction Register causes the

corresponding pin to be an output, and any bit set

to 0 causes it to be an input. The default mode for

all port pins is input.

Table 43. Port Pin Direction Control, Output

Enable P.T. Not Defined

Table 44. Port Pin Direction Control, Output

Enable P.T. Defined

Table 45. Port Direction Assignment Example

Figure 29 and Figure 31 show the Port Architec-

ture diagrams for Ports A/B/C and E/F/G, respec-

tively. The direction of data flow for Ports A, B, C

and F are controlled not only by the direction reg-

ister, but also by the output enable product term

from the PLD AND Array. If the output enable

product term is not active, the Direction Register

has sole control of a given pin’s direction.

An example of a configuration for a Port with the

three least significant bits set to output and the re-

mainder set to input is shown in Table 45. Since

Port D only contains four pins, the Direction Reg-

ister for Port D has only the four least significant

bits active.

Drive Select Register.

The Drive Select Register

configures the pin driver as Open Drain or CMOS

for some port pins, and controls the slew rate for

the other port pins. An external pull-up resistor

should be used for pins configured as Open Drain.

A pin can be configured as Open Drain if its corre-

sponding bit in the Drive Select Register is set to a

1. The default pin drive is CMOS.

(The slew rate is a measurement of the rise and

fall times of an output. A higher slew rate means a

faster output response and may create more elec-

trical noise. A pin operates in a high slew rate

when the corresponding bit in the Drive Register is

set to 1. The default rate is slow slew.)

Table 46 shows the Drive Register for Ports A, B,

C, D, E, F and G. It summarizes which pins can be

configured as Open Drain outputs and which pins

the slew rate can be set for.

RD

PSEL0

PSEL1

PSEL

VM REGISTER BIT 7

WR

PA0-PA7

D0-D7

DATA BUS

AI02886

Direction Register Bit

Port Pin Mode

0

Input

1

Output

Direction

Register Bit

Output Enable

P.T.

Port Pin Mode

0

0

Input

0

1

Output

1

0

Output

1

1

Output

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0

0

0

0

0

1

1

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD4235G3-A-15M | CAP 0.68UF 20V 10% TANT SMD-3216-18 TR-13-PL SN/PB5% |

| PSD4235G3-A-15MI | CAP 0.68UF 20V 10% TANT SMD-3216-18 TR-13-PL SN100% |

| PSD4235G3-A-15U | CAP 0.68UF 20V 10% TANT SMD-3216-18 TR-13-PL SN100% |

| PSD4235G3-A-15UI | Flash In-System-Programmable Peripherals for 16-Bit MCUs |

| PSD4235G3-B-15J | Flash In-System Programmable ISP Peripherals For 16-bit MCUs 5V Supply |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD4256G6V-10UI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 3.3V 8M 100ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD4-36 | 制造商:Tamura Corporation of America 功能描述: |

| PSD-45 | 制造商:MEANWELL 制造商全稱:Mean Well Enterprises Co., Ltd. 功能描述:45W DC-DC Single Output Switching Power Supply |

| PSD-45_11 | 制造商:MEANWELL 制造商全稱:Mean Well Enterprises Co., Ltd. 功能描述:45W DC-DC Single Output Switching Power Supply |

| PSD-45A-05 | 功能描述:線性和開關(guān)式電源 30W 5Vout 6A Input 9.2-18VDC RoHS:否 制造商:TDK-Lambda 產(chǎn)品:Switching Supplies 開放式框架/封閉式:Enclosed 輸出功率額定值:800 W 輸入電壓:85 VAC to 265 VAC 輸出端數(shù)量:1 輸出電壓(通道 1):20 V 輸出電流(通道 1):40 A 商用/醫(yī)用: 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風(fēng)格:Rack 長度: 寬度: 高度: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。