- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361292 > QL5064-33APB484I BUS CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | QL5064-33APB484I |

| 英文描述: | BUS CONTROLLER |

| 中文描述: | 總線控制器 |

| 文件頁數(shù): | 28/37頁 |

| 文件大?。?/td> | 806K |

| 代理商: | QL5064-33APB484I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

QL5064 QuickPCI Data Sheet

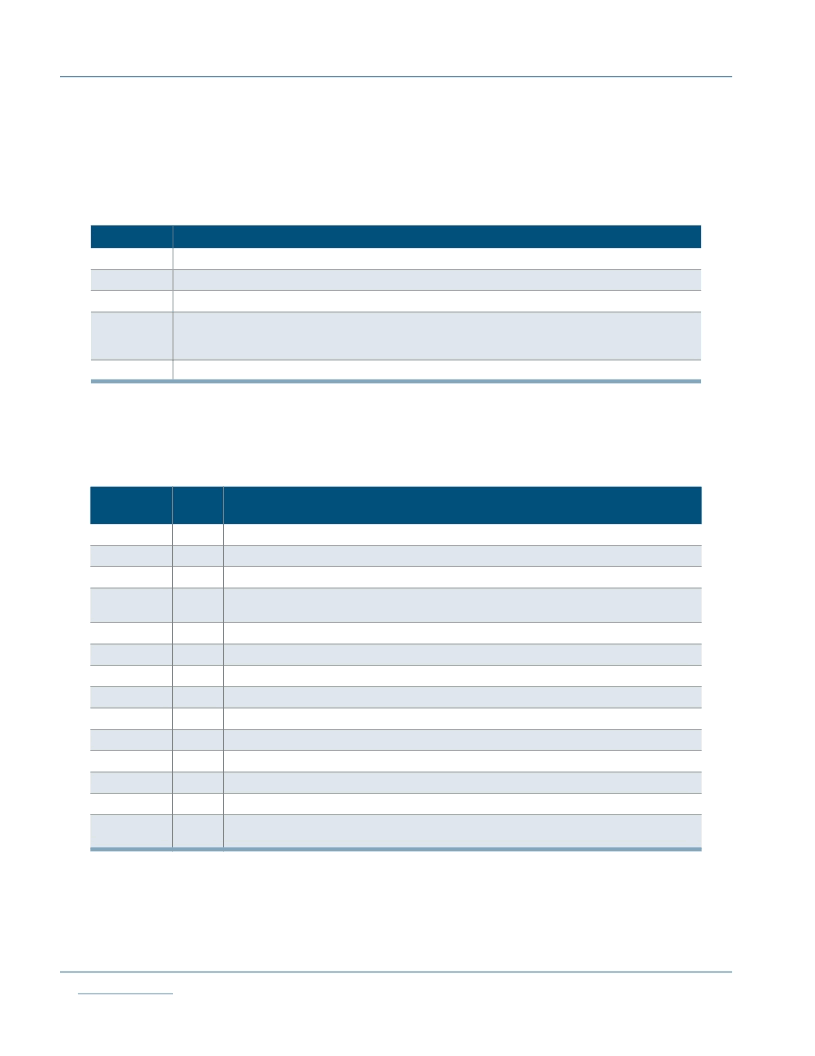

22.0 QL5064 Pin Type Descriptions

The QL5064 Device Pins are indicated in the table below. These are pins on the device, some of which

connect to the PCI bus, and others that are programmable as user I/O.

NOTE:

Signal names which end with the character ‘N’ should be considered active-low

(for example, Mst_IRDYN).

Table 16: Pin Type Descriptions

Type

Description

IN

Input. A standard input-only signal

OUT

Totem pole output. A standard active output driver

T/S

Tri-state. A bi-directional, tri-state input/output pin

S/T/S

Sustained Tri-state. An active low tri-state signal driven by one PCI agent at a time. It must be driven high for

at least one clock before being disabled (set to Hi-Z). A pull-up needs to be provided by the PCI system central

resource to sustain the inactive state once the active driver has released the signal.

O/D

Open Drain. Allows multiple devices to share this pin as a wired-or.

Table 17: Pin / Bus Names and Functions

Pin/Bus

Name

Type

Function

VCC

IN

Supply pin. Tie to 3.3V supply.

VCCIO

IN

Supply pin for I/O. Set to 3.3V for 3.3V I/O, 5V for 5.0V compliant I/O

GND

IN

Ground pin. Tie to GND on the PCB.

T/GND

IN

Thermal Ground. Used to dissipate heat from the device. Tie to GND on

the PCB.

I/O

T/S

Programmable Input/Output/Tri-State/Bi-directional Pin.

I/GCLK

IN

Programmable Input-Only or Global Clock Pin. Tie to VCC or GND if unused.

I/ACLK

IN

Programmable Input-Only or Array Clock Pin. Tie to VCC or GND if unused.

TDI

IN

JTAG Data In. Tie to VCC if unused.

TDO

OUT

JTAG Data Out. Leave unconnected if unused.

TCL

IN

JTAG Clock. Tie to GND if unused.

TMS

IN

JTAG Test Mode Select. Tie to VCC if unused.

TRSTB

IN

JTAG Reset. Tie to GND if unused.

STM

IN

QuickLogic Reserved pin. Tie to GND on the PCB.

FLOAT

OUT

Test Data Out pin for QuickLogic use only. Must be isolated and floating at

all times

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QL5064-33BPB456C | BUS CONTROLLER |

| QL5064-33BPB456I | BUS CONTROLLER |

| QL5064-33BPB484C | BUS CONTROLLER |

| QL5064-33BPB484I | BUS CONTROLLER |

| QL5064-66APB456C | BUS CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QL5064-66APS484C-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66APS484I-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66BPS484C-5725 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484C-5616 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484I-5612 | 制造商:QuickLogic Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。