- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361297 > QL901M-6PS680 (Electronic Theatre Controls, Inc.) SOCKET, PCB, RIGHT ANGLE, 26WAY; Connector type:Wire-to-Board; Gender:Socket; Ways, No. of:26; Pitch, lead:2.54mm; Termination method:Solder; Material, contact:Copper alloy; Plating, contact:0.3u Gold over 2u Nickel; Rows, No. of:2; RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號: | QL901M-6PS680 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | SOCKET, PCB, RIGHT ANGLE, 26WAY; Connector type:Wire-to-Board; Gender:Socket; Ways, No. of:26; Pitch, lead:2.54mm; Termination method:Solder; Material, contact:Copper alloy; Plating, contact:0.3u Gold over 2u Nickel; Rows, No. of:2; RoHS Compliant: Yes |

| 中文描述: | QuickMIPS ESP家庭 |

| 文件頁數(shù): | 27/37頁 |

| 文件大小: | 432K |

| 代理商: | QL901M-6PS680 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

QL901M QuickMIPS Data Sheet Rev B

27

6.0 Pin Descriptions

Table 27

defines the QuickMIPS chip pins.

Table 27: Pin Descriptions

Pin

I/O

Function

PCI Signals

PCI_AD[31:0]

I/O

PCI Address and Data. PCI_AD[31:0] contain the multiplexed address and data. A bus transaction

consists of a single address phase (or two address phases for 64-bit addresses) followed by one or

more data phases. The QuickMIPS chip supports both read and write bursts.

The address phase occurs in the first clock cycle when PCI_FRAME_n is asserted. During the address

phase, PCI_AD[31:0] contain a 32-bit physical address. For I/O, this is a byte address; for configuration

and memory, it is a DWORD (32-bit) address. During data phases, PCI_AD[7:0] contain the least-

significant byte, and PCI_AD[31:24] contain the most-significant byte.

Write data is stable and valid when PCI_IRDY_n is asserted; read data is stable and valid when

PCI_TRDY_n is asserted. Data is transferred when both PCI_IRDY_n and PCI_TRDY_n are asserted.

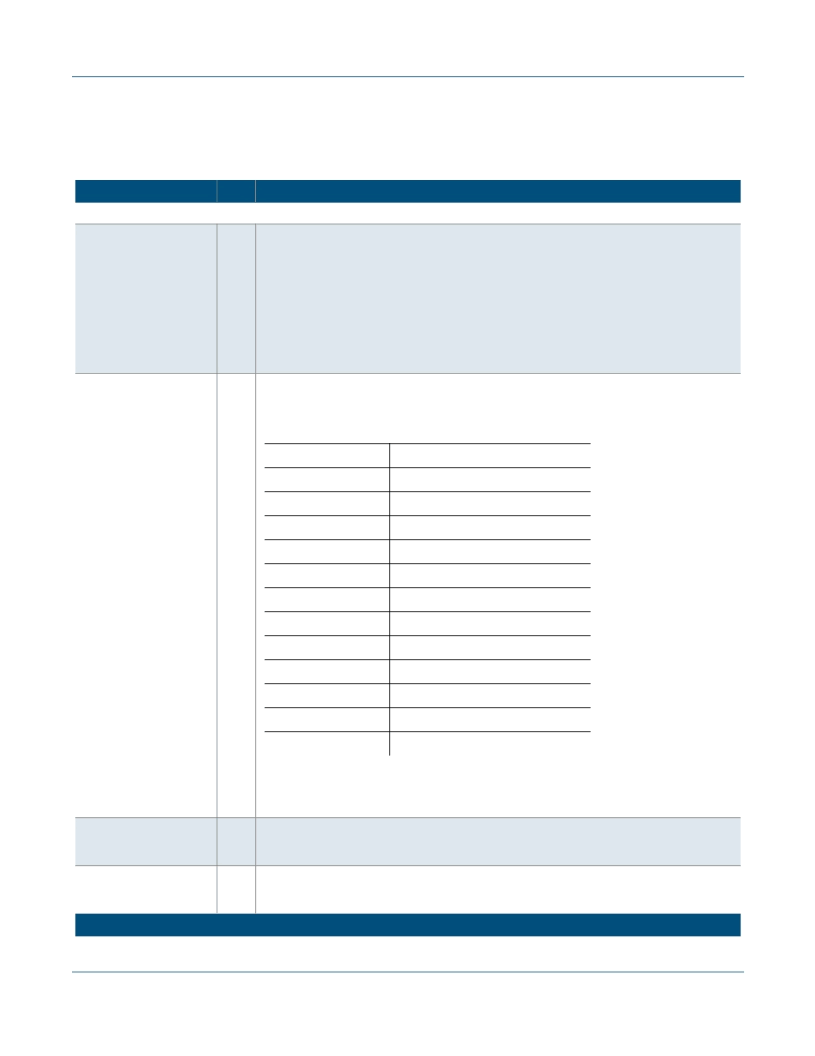

PCI_C_BE_n[3:0]

I/O

Bus Command and Byte Enables. Bus commands and byte enables are multiplexed on

PCI_C_BE_n[3:0]. During the address phase of a transaction (PCI_FRAME_n is asserted),

PCI_C_BE_n[3:0] define the bus command as shown in the following table (only valid combinations are

shown).

During each data phase, PCI_C_BE_n[3:0] are byte enables. The byte enables are valid for the entire

data phase and determine which byte lanes contain meaningful data. PCI_C_BE_n[0] applies to byte

0 (PCI_AD[7:0]) and PCI_C_BE_n[3] applies to byte 3 (PCI_AD[31:24]).

PCI_DEVSEL_n

I/O

PCI Device Select. When asserted low, PCI_DEVSEL_n indicates the driving device has decoded its

address as the target of the current access. As an input, PCI_DEVSEL_n indicates whether any device

on the bus has responded.

PCI_FRAME_n

I/O

PCI Cycle Frame. The current master asserts PCI_FRAME_n to indicate the beginning and duration of

a bus transaction. While PCI_FRAME_n is asserted, data transfers continue. When PCI_FRAME_n is

deasserted, the transaction is in the final data phase or has completed.

(Sheet 1 of 6)

PCI_C_BE_n[3:0]

Bus Command

0000

Interrupt Acknowledge

0001

Special Cycle

0010

I/O Read

0011

I/O Write

0110

Memory Read

0111

Memory Write

1010

Configuration Read

1011

Configuration Write

1100

Memory Read Multiple

1101

Dual Address Cycle

1110

Memory Read Line

1111

Memory Write and Invalidate

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QL901M-6PS680C | Electrical Spring Connector; Contact Termination:Twist On; Wire Size (AWG):14-10; Body Material:Flame retardant nylon; Contact Material:Spring Steel; Pack Quantity:100; Series:512; Size:2-#18 up to 5-#12; Voltage Rating:600V RoHS Compliant: Yes |

| QL901M-6PS680I | QuickMIPS ESP Family |

| QLA694B-2G | PCB MOUNT LED INDICATORS |

| QLA694B-2H | PCB MOUNT LED INDICATORS |

| QLA694B-2I | PCB MOUNT LED INDICATORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QL901M-6PS680C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:QuickMIPS ESP Family |

| QL901M-6PS680I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:QuickMIPS ESP Family |

| QL902M200-2PS544C-5654M | 制造商:QuickLogic Corporation 功能描述: |

| QL902M200-2PS544C-5994 | 制造商:QuickLogic Corporation 功能描述: |

| QL90F7S-A | 制造商:ROITHNER 制造商全稱:ROITHNER 功能描述:LASER DIODE SPECIFICATIONS FOR APPROVAL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。